主题中讨论的其他器件:ADC-WB-BB、 DAC3484EVM、 CDCE62005、 DAC3484、 CDCM7005

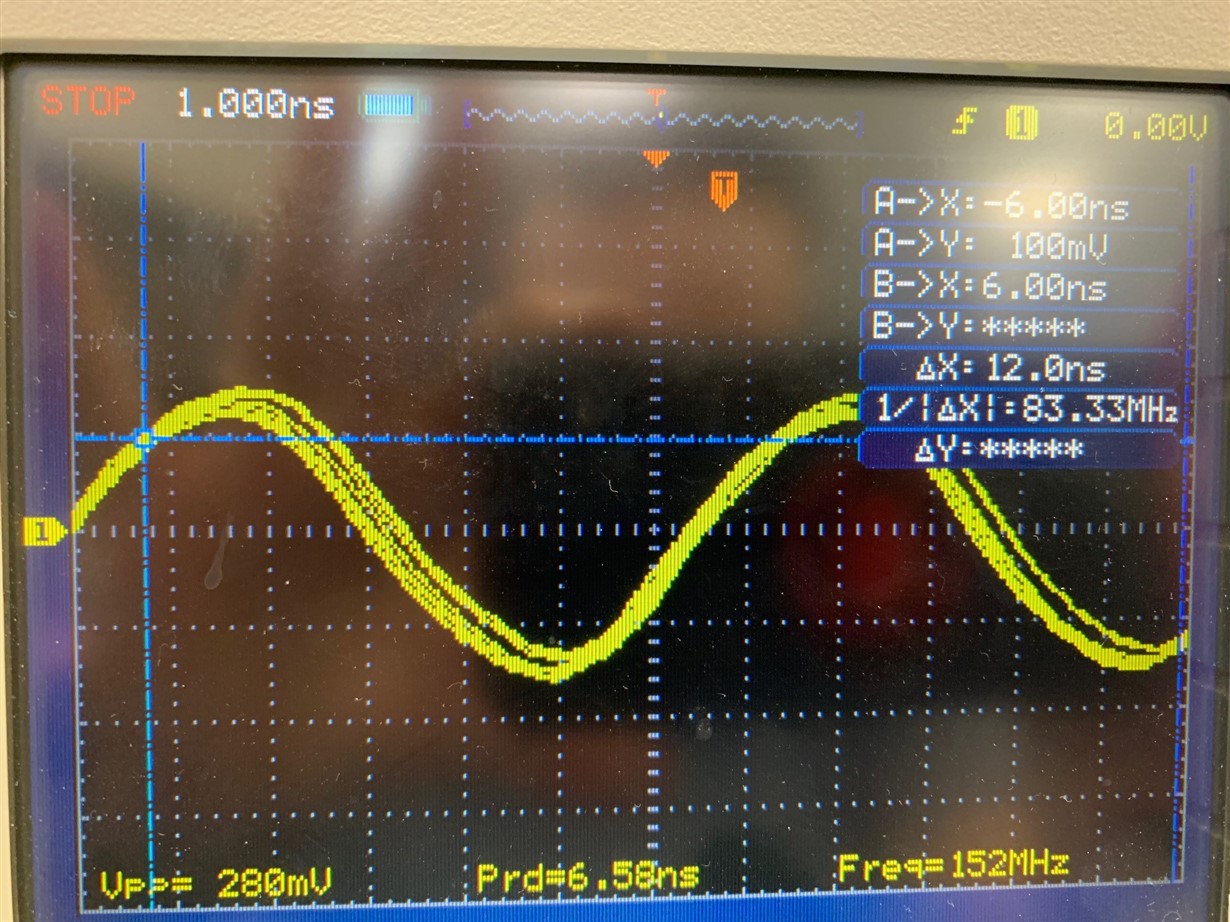

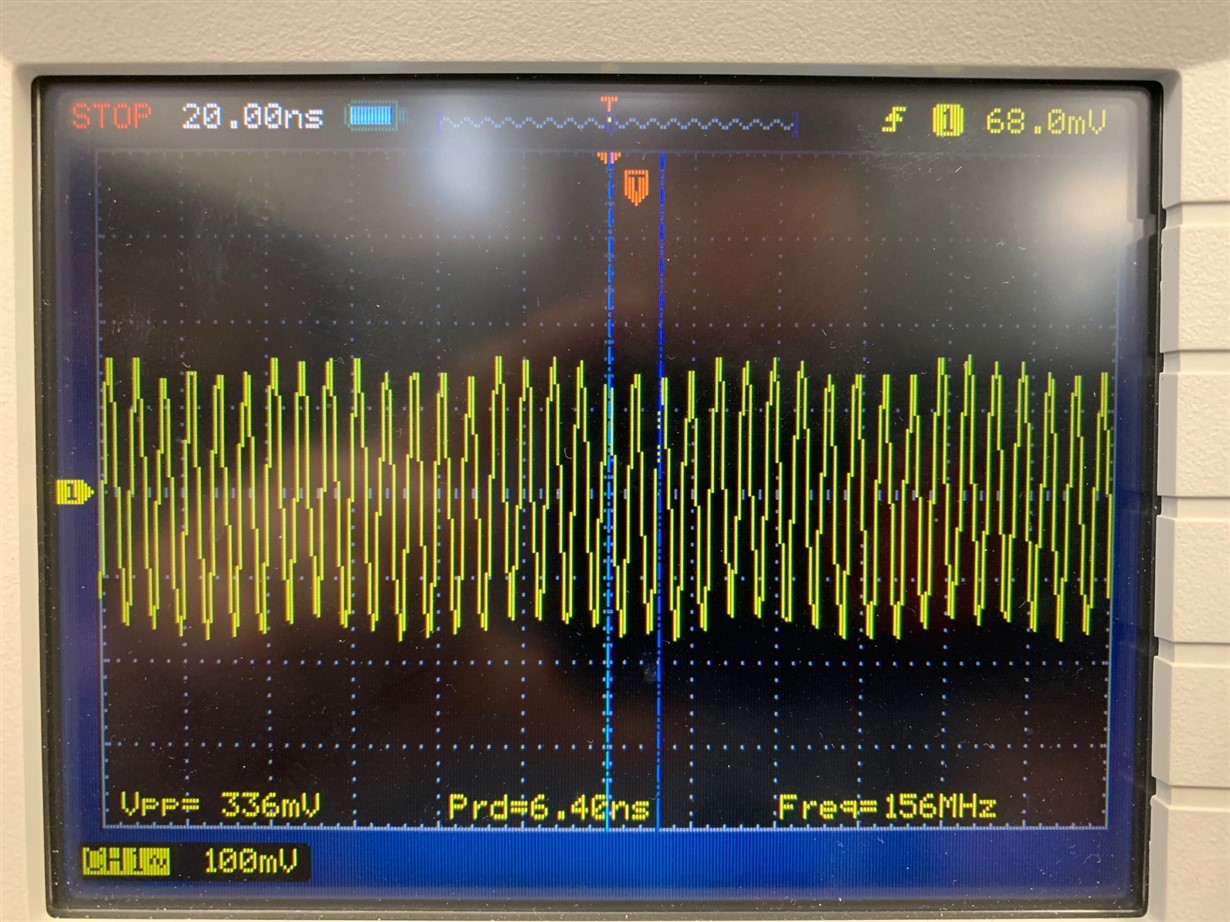

我将驱动来自 CLKout0/CLKout0*的1个1Vpp 153.6MHz LVPECL20 +/-信号、并连接到连接到 DAC3484EVM 的 J9 CLKIN 输入的 ADC-WB-BB 平衡-非平衡变压器。 该信号衰减为24mVpp 信号、该信号位于板载 CDCE62005 PRI REF+输入的200mV 直流偏置上。 我不认为这个外部时钟正通过时钟芯片提供返回 FPGA 的时钟输出。 FPGA_CLKOUTP 和 FPGA_CLKOUTN 上的输出均为2.72VDC。 我已经连接了 DAC3484EVM 寄存器设置文件。