请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CDCE949-Q1 您好!

在我的设计中 ,CDCE949-Q1输入是25MHz 晶振,Y3输出也是25MHz,用于以太网 PHY。 在数据表中、CDCE949-Q1输出时钟抖动为峰峰值周期抖动:μ s

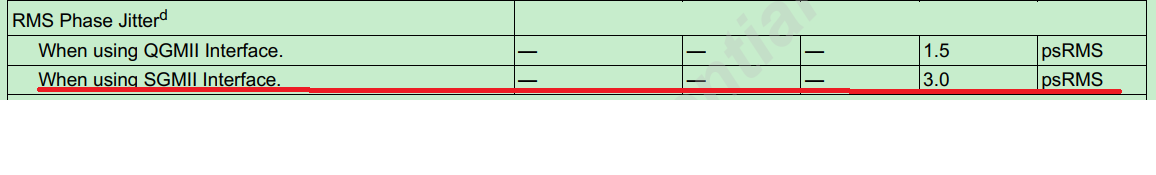

但 Ehternet PHY 输入时钟抖动参数是 RMS 相位抖动、应为<3.0ps

那么、CDCE949-Q1输出相位抖动是否能够满足这一要求? CDCE949-Q1输出时钟的相位抖动值是多少?

谢谢你。

此致。

Gavin