Other Parts Discussed in Thread: LMX2491

您好!

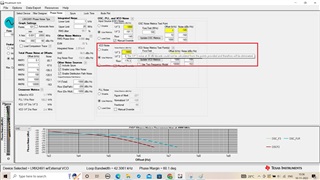

使用外部 VCO 和环路滤波器时、我尝试分析整个 PLL 的相位噪声、我有以下问题:

1)根据理论、PLL 的相位噪声将跟随环路带宽内的 OCXO (基准振荡器)噪声。 但我在仿真 LMX2491时无法看到结果。

2) 2)根据理论计算、OCXO (100MHz)的相位噪声为-155dBc/Hz @ 1KHz 偏移;我想了解 PLL 相位噪声在1KHz 偏移时没有提高到-97dBc/Hz 以上的原因。

3) 3)我无法加载 OCXO 和 VCO 相位噪声数据、因为错误显示"Offset violates 3 point modemption (偏移违反3点模型假设)"和"1/f^3 noise could not be calculated (无法计算1/f 3噪声)"。

请指导我评估设计的正确性

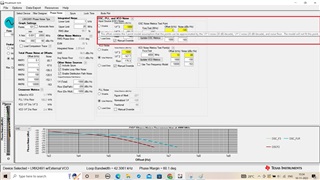

(这不是正确的配置)

(这不是正确的配置)