大家好、我们设计了一个 IF/RF 合成器板、其中有两个 PLL、即 LMX2581、一个在射频侧、一个在 IF 侧... 在其中一个 PLL 中、我们尝试使用寄存器 R0至 R15中的以下设置生成148.4MHz 的频率、

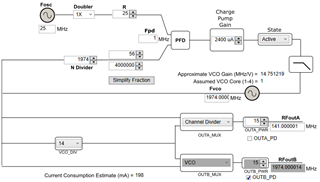

我们使用25MHz 作为 OSCin、FPD 也是25MHz PLL_N 我们将设置为83.104、分数设置为104/100 DIV2或 VCO/DIV 设置为14

我们得到的输出为148.43751MHz、而不是148.4... 根据 EVM 设计使用环路滤波器,您能不能建议我们如何实现1Hz 的精确148.400001MHz 的分辨率,比例的微小变化不会导致频谱分析仪中测量的频率输出发生任何变化。

此外、我们尝试在 PLL_N = 90.0、Fraction = 90/100、VCO_DIV = 16和 FPD = 25MHz 以及 OSCin = 25MHz 的情况下生成145.15625、但我们得到的输出为145.3125MHz、更改比例不会对频率输出产生任何影响。

我们使用 TCXO SiT5356AI-FQ-33E0-25.000000X (SiTime)

为进一步提高分辨率和精度、我们应进一步研究封装方框图和原理图、以供您参考和使用。

请注意、我们对 PLL 的原理图进行了一些更改、使环路滤波器与 EVM 相同

如果信息不充分或您需要任何其他信息来建议/建议我们、请告知我们