主题中讨论的其他器件:LMK05318B、

我们需要生成一些频率---- 30.72MHz 和6.912MHz,频率范围为100Hz。 该100Hz 时钟将生成并作为 LMK05318BEVM 的输入。

但我们无法生成所需的频率。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们需要生成一些频率---- 30.72MHz 和6.912MHz,频率范围为100Hz。 该100Hz 时钟将生成并作为 LMK05318BEVM 的输入。

但我们无法生成所需的频率。

您好 Gurunath、

这应符合您的要求。

e2e.ti.com/.../LMK05318B_5F00_100Hz-in.tcs

此致、

维森特

尊敬的 Vicente:

是的、当我启用输出通道同步时、在示波器上看不到输出信号。

我还想在此强调一些要点:

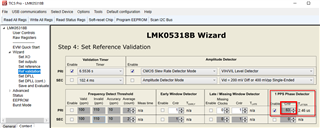

1.对于"LMK05318B_100Hzin.TCS"配置文件、我得到以下错误"DPLL 环路带宽必须小于 PRIREF/SECREF 频率"。 我应该配置哪种 LBW 值?

2.我正在使用 LMK05318B EVM 用户指南中提到的默认跳线配置检查时钟输出。 如果我更改任何跳线配置以实现两个输出频率的输出同步和相位对齐、

3.仅在5MHz 与 PRI_REF 的不同配置和10MHz 的输出配置下才能观察到输出同步。 对于任何其他频率配置、输出频率保持异相。

此致、

Akanksh

您好、Akanksh、

此致、

Jennifer

您好、Jennifer、

我尝试了48.0048 MHz 的配置文件、但无法获得输出同步。 因为目前尚不容易获得12.8MHz 输出。 我能否将12MHz 晶体输入用于时钟(EVM 上需要进行任何硬件更改)? 10MHz SE 输入可用、但无法通过向导将其配置为 XO 频率。

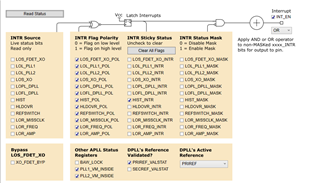

读取状态寄存器时、HLDOVR_INTR 显示为高电平。 可能的原因是什么。 R 分频器和 FB 分频器显示为 HIGH (LED 显示屏)。

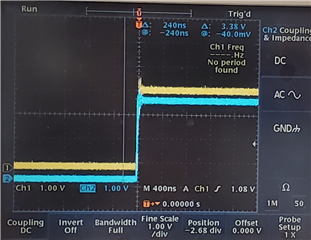

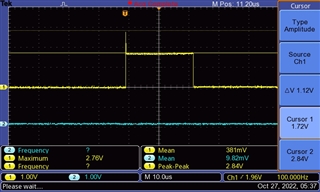

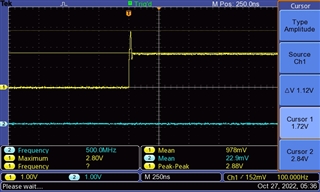

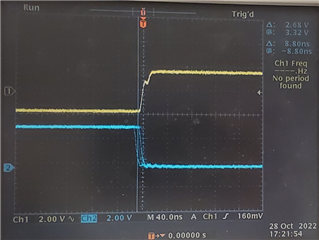

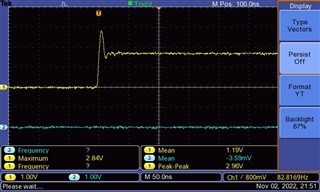

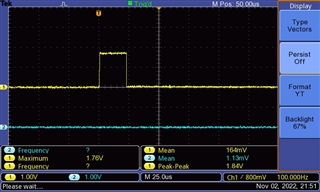

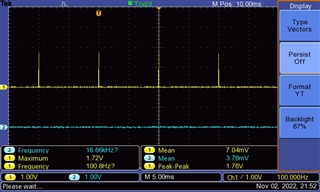

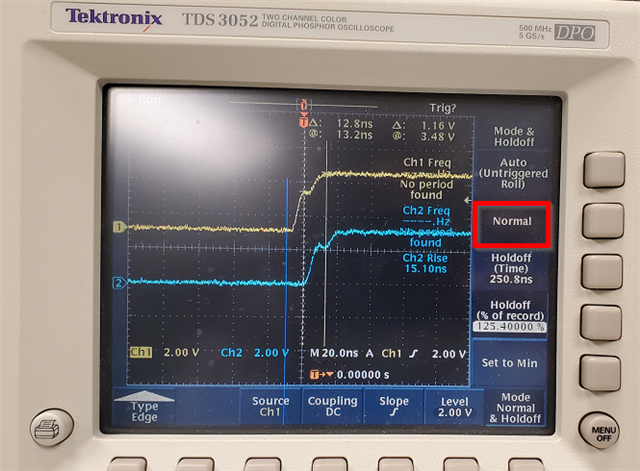

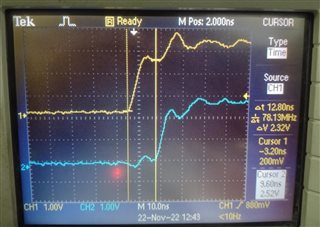

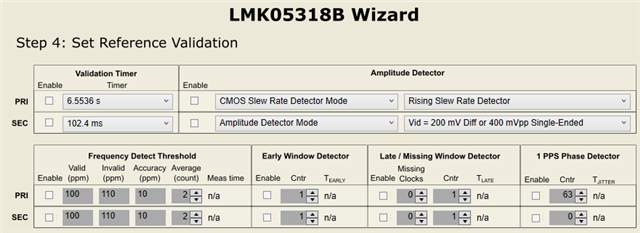

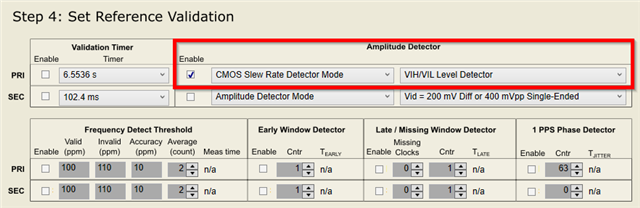

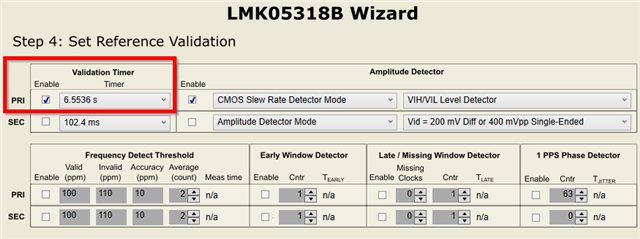

我还想知道基准验证是否与正在使用的100Hz 基准的 DPLL 基准验证设置相关。 导通持续时间为20us;峰值过冲电压- 2.84V、高电压为1.8V。随附示波器图像。

您好、Akanksh、

让我澄清我之前的帖子和您的问题:

此致、

Jennifer

您好、Jennifer、

由于 时钟发生器不可用、我们目前正在尝试26 MHz 振荡器、0.5 ppm 精度。 根据所需 XO 精度的计算、它在限制范围内。 因此、是否可以将此时钟用于共享的配置文件? DPLL 脚本之后、在检查状态时、HLDOVR_INTR 标志设置为高电平、DPLL 的活动基准进入 HOLDOVER。 R 分压器和 FB 分压器的电压在整个过程中显示为高电平。 是由于基准信号问题?

从通用芯片生成的100Hz 时钟(将用于最终应用)的波形图如下:

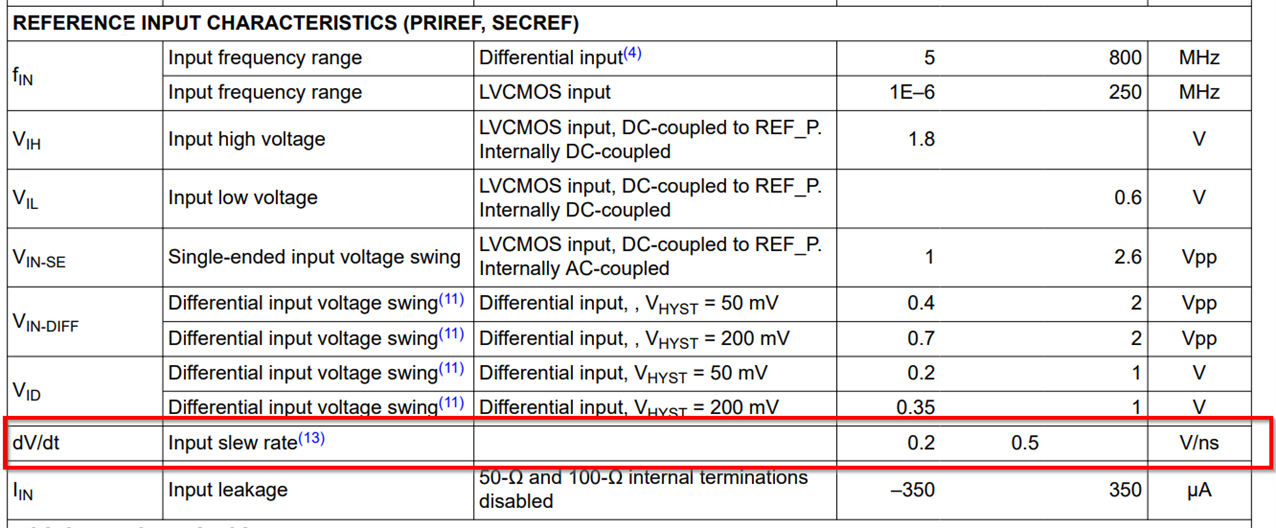

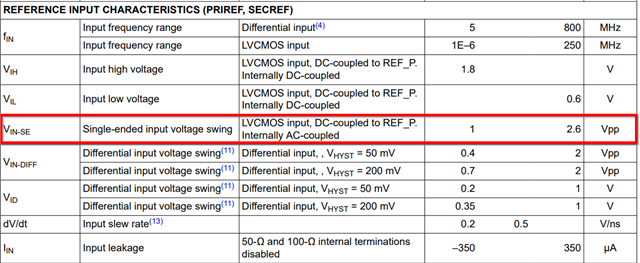

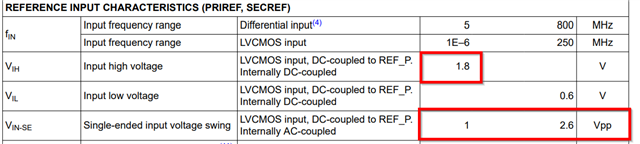

a:由于峰值电压达到~ 3V、是否会导致基准锁定问题? 因为数据表中的表格显示的最大值为2.6Vpp。

B.信号的导通周期为~ 22us。

C.时间周期恒定为10ms。

此致

Akanksh S

您好、Jennifer、

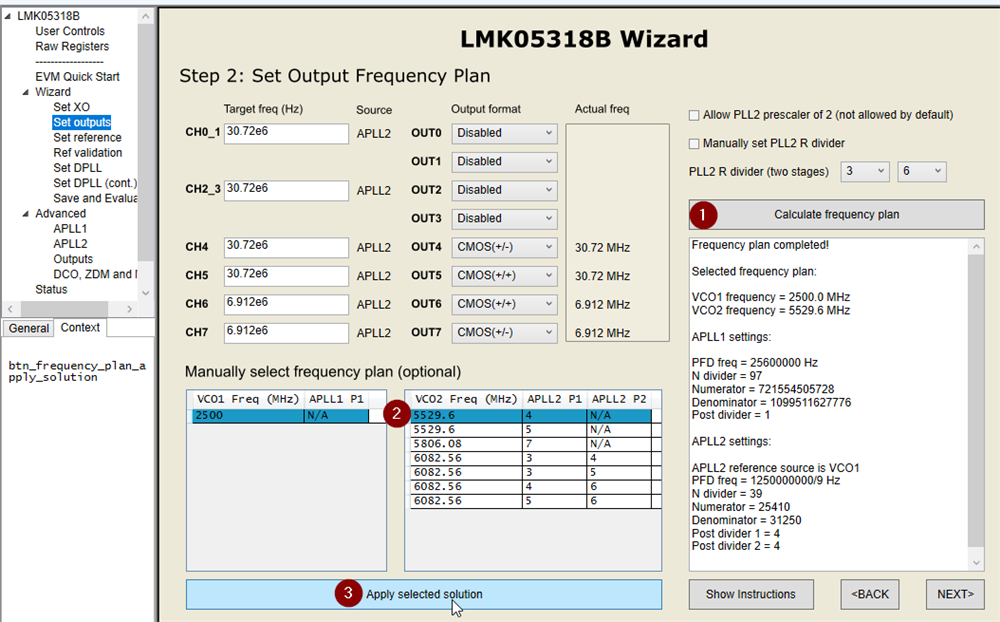

我使用时钟发生器生成12.8MHz 输出。 即使在共享配置文件的20分钟后("e2e LMK05318B_XO = 12.8 MHz_PRIREF= 100Hz_OUT=30.72和6.912 MHz_OCT 21 2022.TCS")、输出锁定也不会发生。 是否应在整个过程中检查 SYNC_SW、或者在5秒内仅执行断言和取消断言就足够了? DPLL PRI_REF 的保持问题似乎可以使用适当的100Hz 时钟解决、但仍无法锁定到输入端。 是否应在"设置输出部分"中手动选择"频率规划"以避免 APLL2 P2后分频器?

尝试不同的方案时: 更改了12.8MHz XO 的 EVM 默认配置文件(使其他参数保持恒定)、使用 PRI_REF (25MHz)观察输入端的输出锁定。

你好、Jennifer。

我们可以使用 APLL1将 PRIREF 锁定为 O/P 时钟。 但仍然使用 APLL2、我们无法锁定。

测试详细信息和我们实现了锁相的 O/P 频率

1)

XO 频率= 12.8MHz

PRIREF 频率= 100Hz

O/P 时钟1频率= 6.25MHz

O/P 时钟2频率= 31.25MHz

2)

XO 频率= 12.8MHz

PRIREF 频率= 100Hz

O/P 时钟1频率= 6.25MHz

O/P 时钟2频率= 25MHz

但我们无法使用 APLL1或 APLL2实现预期频率的30.72MHz 和6.912MHz 锁相。

请尽快向我们发送配置文件、以确定哪个相位锁定我们的预期频率。

客户无法继续前进、因为他正在等待预期频率的锁相。

您好、Akanksh、

您好、Akanksh、

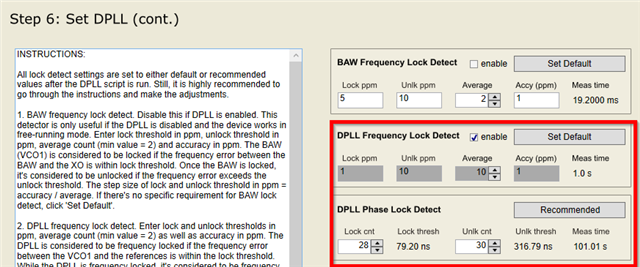

最好听 LOPL_DPLL 清零。 由于 DPLL LBW 较低(0.01Hz)、锁相(并报告)所需的时间要长得多。

我还有类似的症状、LOFL_DPLL 持续切换。 这是我仍在研究的问题 、因为器件未正确报告 DPLL 频率锁定检测、实际上不是 DPLL 频率锁定的问题。 如果 LOPL_DPLL = 0、DPLL 将被锁定。

此致、

Jennifer

Akanksh 、Gurunath、

从我们11月17日的呼叫中、您请求了 PRIREF = 1Hz、10Hz 和1MHz 的配置以输出 6.912 MHz 和30.72 MHz。

今天、我可以提供以下配置:

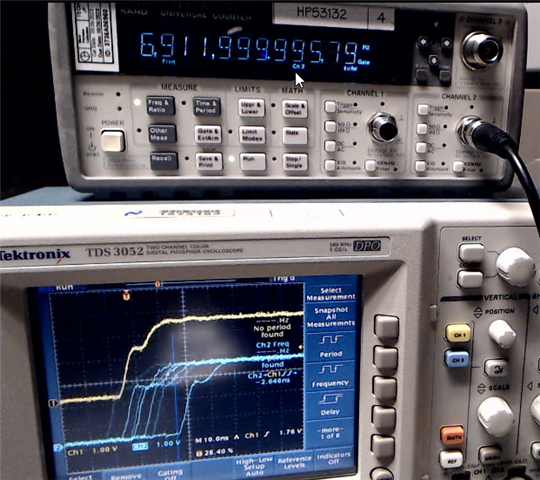

我已通过状态页面和 DPLL R & FB 分频器确认 DPLL 锁定。 并确认 频率在频率计数器上符合预期。

请告诉我、如果您成功地使用这些配置实现了连续 DPLL 锁定。

此致、

Jennifer

您好、Jennifer、

我们尝试了共享的配置、观察结果如下:

编辑:突出显示 PRI_REF 最后一条消息中的拼写错误。

Akanksh、

一些意见和问题:

此致、

Jennifer

您好、Jennifer、

以下是我对问题的回答:

1。对于 PRI_REF = 1MHz (前一响应中的拼写错误为1pps)

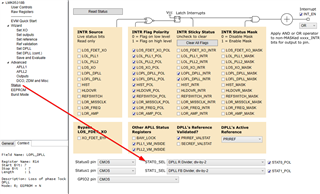

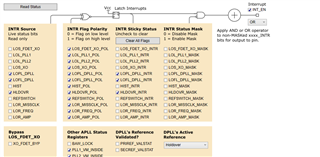

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134"]请注意,必须手动清除中断标志。是的、我选择了"清除所有标志"并通过单击"读取状态"选项获得标志状态。

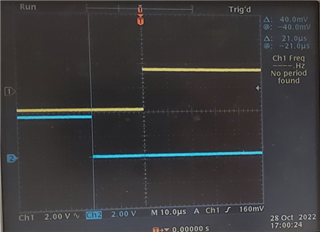

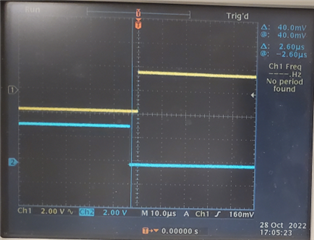

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134">对于 DPLL R 和 FB 分频器、您的意思是"保持锁定状态"? 您是否能够锁定在本例中、R 和 FB 分频器的相距为13ns。 该图如下所示:

"保持锁定状态"意味着上述波形不会相互漂移、 Δt μ s 处于10ns 至14ns 范围内。

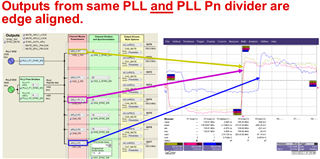

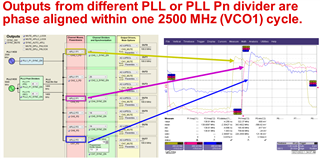

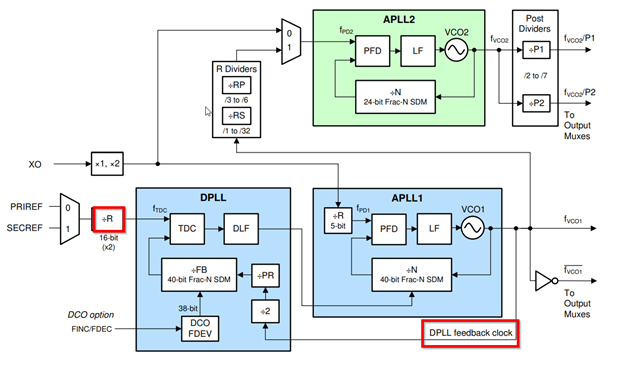

[引用 userid="451450" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134]DPLL FB 分频器来自 VCO 输出。 这个 FB 分频器代表 OUT 信号、这是因为在 VCO 输出之后、只有 PLL PN 分频器和输出通道分频器。 这意味着、如果 DPLL R 和 FB 分频器上存在锁定、则 PRIREF 和输出上应存在锁定。 [/报价]但考虑到我们的输出频率为6.912 MHz 和30.72 MHz、它们来自 VCO2输出。

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134"]您如何定义 PRIREF 和输出"未锁定"?[/quot]我们设置 PRI_REF 信号触发源(CH1)、并且 CH2连接到 EVAL 板的 OUT7_P。 当 PRI_REF 的上升沿与 OUT7_P 信号的上升沿对齐时、会确认两个信号之间的锁定。 通道2保持解锁至触发源(已连接视频文件)。

e2e.ti.com/.../WhatsApp-Video-2022_2D00_11_2D00_22-at-12.58.22-PM.mp4

根据观察到的25MHz (CH2上)和 PRI_REF 1MHz (CH1上) CH7_P APLL1输出锁定至输入、并且共享相同的配置文件:

e2e.ti.com/.../WhatsApp-Video-2022_2D00_11_2D00_22-at-1.05.29-PM.mp4

[引用 userid="451450" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134]\n 可能是触发问题? 如果您在范围[/quot]上有此选项、则可以尝试将其设置为"Normal"模式是的、在触发菜单中、模式被设定为"正常"模式。

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134">您如何采购1Hz? 请提供器件型号。1MHz 和1Hz PRI_REF 时钟的时钟源来自 CG635合成时钟发生器、CMOS 1.8V 输出。

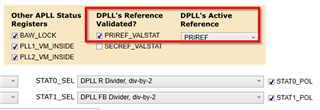

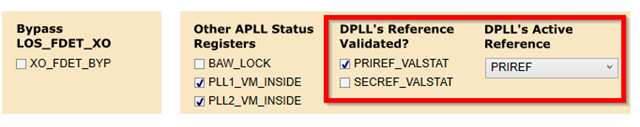

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134"] PRIREF_VALSTAT 是否为1?[/quot]是的、PRIREF_VALSTAT=1。

这是与1 PPS 相关的响应、即 PRIREF (由于拼写错误、在之前被提到为1MHz)。

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134">您如何采购1MHz? 请提供器件型号。1MHz PRI_REF 时钟的源来自 CG635合成时钟发生器。

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134">此输入的信号电平是多少? 请确保输入符合规格[/报价]信号电平为1.8V DC。

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4416134 #4416134"] PRIREF_VALSTAT 是否为1?[/quot]是的、PRIREF_VALSTAT = 1。

是否能够针对10Hz 基准输入获得输出的基准锁定。 如果可能、您可以共享配置文件吗?

您好、Akanksh、

以下是我们呼叫的后续步骤:

此致、

Jennifer

您好、Jennifer、

我们可以根据会议讨论的过程为1pps 时钟基准(来自 CG635)生成输入到输出时钟的相位锁定。

现在、我们的要求是锁定从我们的定制芯片生成的1pps 时钟、该时钟的最大可能时钟周期变化为1±0.00474秒、因此频率计数器也会观察到相应的频率变化。 在使用该时钟作为参考时、PRIREF 被选择~5秒、并在接下来的5秒内保持解锁状态。

在这里 、PRIREF_VALSTAT = 1一直被确保到前一个应答中提到的4.c。

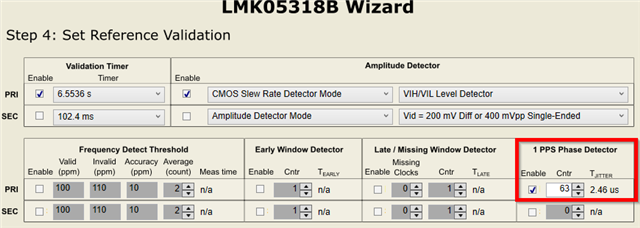

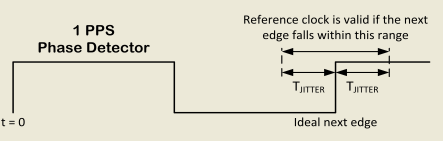

[引用 userid="451450" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1161390/lmk05318bevm-ticspro-sw/4431823 #4431823"]启用验证计时器。 如果输入在指定时间内保持有效、它将报告 PRIREF_VALSTAT = 1。 在此状态下、振幅检测器必须在~6s 内有效才能报告有效[/QUERP]启用1pps 相位检测器后、DPLL 基准将保持从 PRIREF 到 HOLDOVER 的切换。

由于 PRIREF_VALSTAT = 1未被确保、我没有尝试修改 LOPL 和 LOFL 阈值。

您好、Jennifer、

我们需要在获取正确的 DPLL LBW 更改以及 PRIREF = 9.9338Hz 对应的配置文件方面提供支持。 对于该频率、我们能够始终保持 PRIREF_VALSTAT = 1 (抖动容差在0.5us 以内)、因此可以将其用作 特定的基准频率。

已使用1Hz 配置文件(LMK05318B_XO = 12.8 MHz_PRIREF= 1PPS_OUT=30.72和6.912 MHz_11月18 2022.TCS)尝试以下操作、并对 PRIREF 进行了更改:

当 LBW = 0.1Hz 时、R 分频器和 FB 分频器永远不会以极快的速度锁定和漂移。

2.如果 LBW = 0.01Hz (与1Hz 配置相同)、即使在观察30分钟后、R 和 FB 也保持2us 的间隔。

此致

Akanksh S

您好、Akanksh、

对延误表示歉意。

对于如此低的 DPLL LBW 频率(~10Hz 等低频要求)、预期锁定时间较慢。

我昨天测试了您的配置、在~1小时后达到了 LOPL=0、但 LOFL 被切换。 在示波器上、频率和相位显然已锁定(6.912 MHz、误差小于1ppm)。 我将设置保持一整晚运行、不会改变。 今天、我检查了输出仍然被锁定、LOPL=0 (LOPL 中断标志也没有被置位)、但是 LOFL 继续切换。 这是 LOFL 报告和错误触发的问题。

通过详细查看 DPLL 寄存器设置、我发现频率锁定计时器值计算正确。

仍然 不清楚为什么 DPLL 报告 LOFL。 我将需要与设计进行讨论、以便进一步了解。

此致、

Jennifer