请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPL5110 尊敬的 E2E:

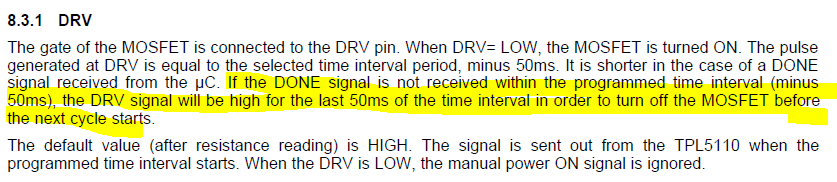

1.我是否可以知道 DELAY/M_DRV 引脚(引脚3)是否连接到 VDD、MOS 是否会强制导通(这意味着 DRV 变为低电平)、对吧?

2.同样的条件是、当 DELAY/M_DRV 引脚(引脚3)连接到 VDD 时 、IC 不会计时、因此不要重置计数、对吧?

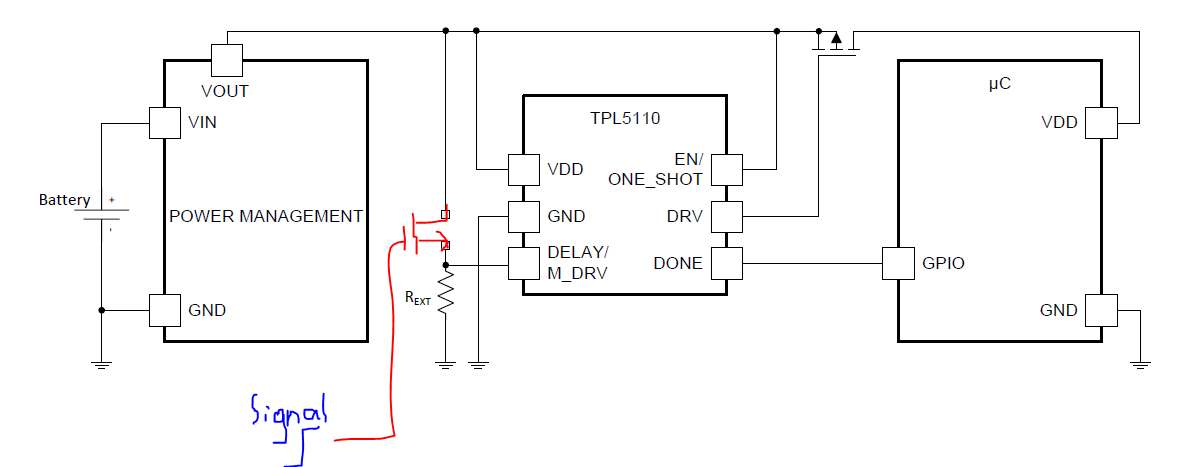

3.我是否可以按如下方式使用该设计?

当信号变为高电平时、DRV 强制变为低电平(MOS 导通)

当信号变为低电平时、引脚3计算时间并开始计数