您好!

我们计划使用您的低抖动时钟缓冲器 CDCLVC1310、通过使用同轴电缆将我们的 LVCMOS SiT5356 TCXO 振荡器(下面给出的数据表链接)输出时钟分配给多个单元。

www.sitime.com/.../SiT5356

在这方面、我们的主要要求如下所示、

时钟输出数:7 (最小值)

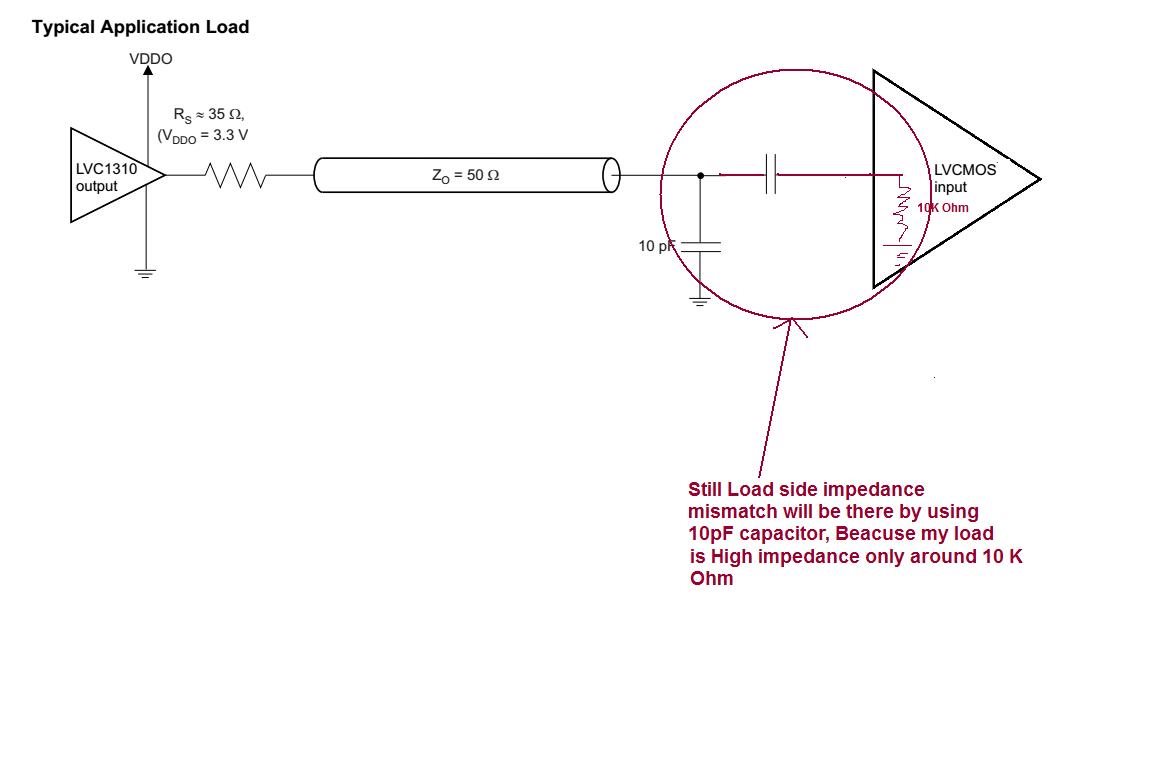

输出驱动:50欧姆同轴电缆连接到其它装置

相位噪声降级:非常小

请查找我们30MHz 输出时的 LVCMOS 振荡器相位噪声(输入到时钟缓冲器)以供您参考。

1Hz 偏移 -70dBc/Hz

10Hz 偏移 -98dBc/Hz

100Hz 偏移 -117dBc/Hz

1kHz 偏移 -138dBc/Hz

10kHz 偏移 -144dBc/Hz

100kHz 偏移 -144dBc/Hz

1MHz 偏移 -157dBc/Hz

5MHz 偏移 -158dBc/Hz

它是否符合我们的上述要求、或者您是否有其他更好的器件满足我们的应用要求?

如果您有任何支持50欧姆负载的应用电路、也建议您使用。

此致、

Sugumar K