请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CDC3RL02 大家好、

我对 CDC3RL02有疑问。 下面是我的基本设置:

- VBATT = 3.3V

- MCLK = 24MHZ 1.8V CMOS

- LDO =未使用/悬空

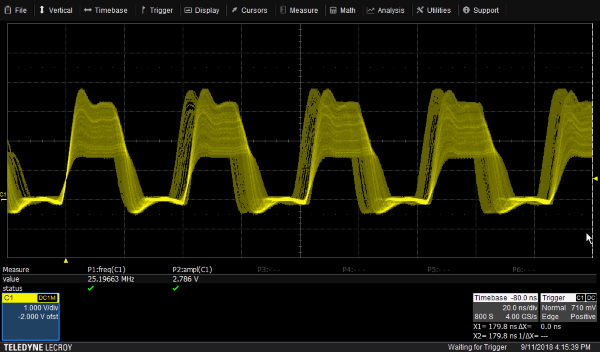

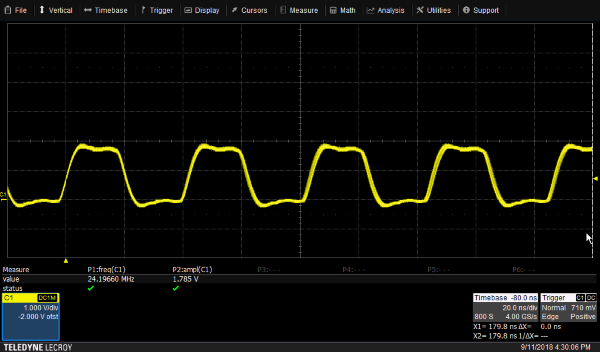

使用上述内容、我的输出看起来像图像1 (下图)。 但是,当我将 VBATT 降至1.8V 时,输出看起来像图像2 (下图)--它清理了相当多的部分。 我有两个问题:

- 我可以在 VBATT = 1.8V 时运行-这种方法是否存在任何潜在的长期问题? 根据数据表、这不在规格范围内、但结果看起来更好。

- 我的问题是否可能与浮动 LDO 有关? 即使 LDO 未使用、也需要将其连接到规格内的电容器吗?

奖励第三个问题-是否有其他可能导致此问题的原因? 提前感谢您的帮助!

当 VBATT = 3.3V 时输出(在3.3V 和1.8V 之间来回弹跳)

2. VBATT = 1.8V 时输出

此致、

Brian Angiel