支持路径:/Product/Development 和故障排除/

您好!

我们最近购买了 LMX2595评估板。

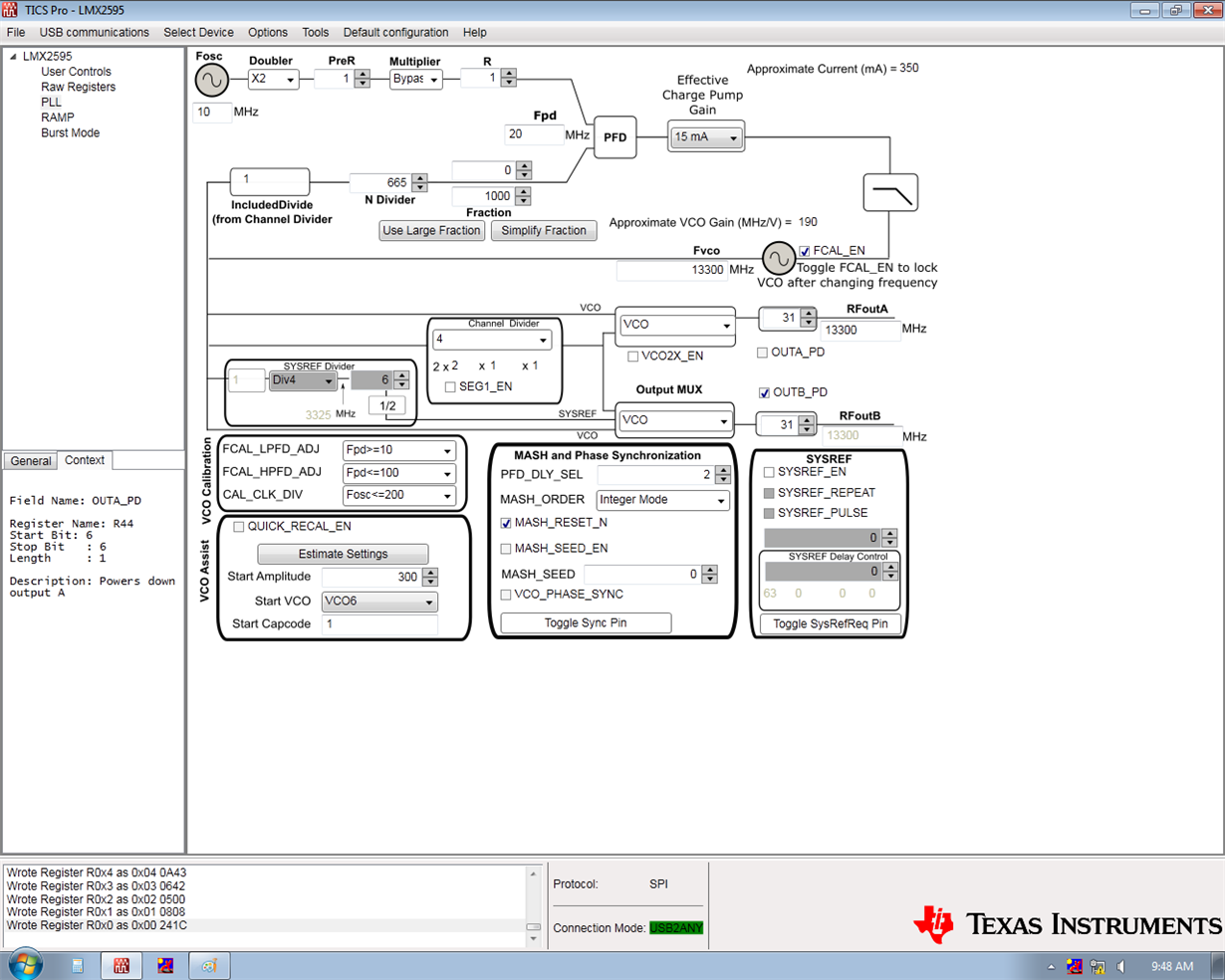

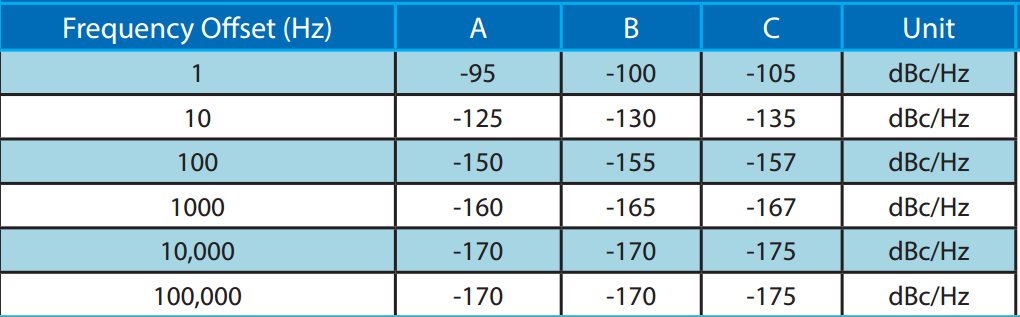

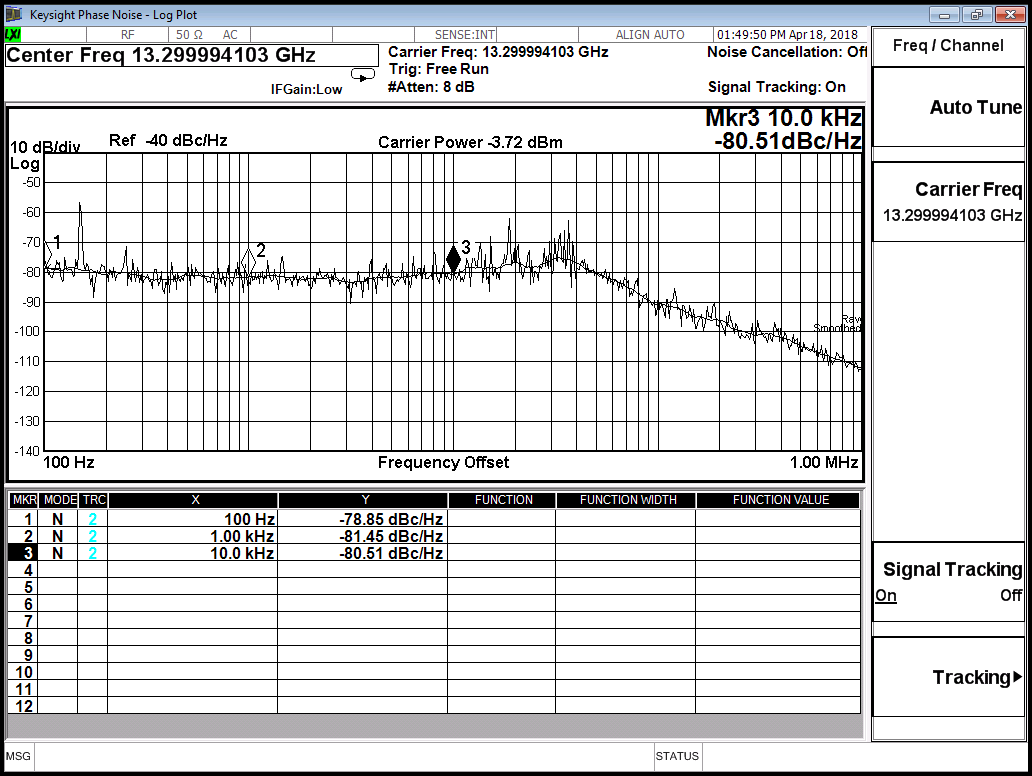

在我们的应用中、我们要求生成参考频率为10MHz 的13GHz…… 我们 使用低噪声倍频器将 PFD 保持为20MHz。我们仅在10kHz 偏移时测量-82dB 的相位噪声。 我们使用非常稳定的 OCXO 作为参考、但我们仍在测量非常高的相位噪声... 请告知问题可能出在哪… 根据数据表进行的计算表明、相位噪声应优于-95dB。 请尽快回复。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

支持路径:/Product/Development 和故障排除/

您好!

我们最近购买了 LMX2595评估板。

在我们的应用中、我们要求生成参考频率为10MHz 的13GHz…… 我们 使用低噪声倍频器将 PFD 保持为20MHz。我们仅在10kHz 偏移时测量-82dB 的相位噪声。 我们使用非常稳定的 OCXO 作为参考、但我们仍在测量非常高的相位噪声... 请告知问题可能出在哪… 根据数据表进行的计算表明、相位噪声应优于-95dB。 请尽快回复。

尊敬的 Dean:

我有2个问题。

在评估板数据表中、对于组装的环路滤波器、提到的带宽为285KHz、但在 PLLatinum 仿真中、为什么要将带宽仿真为49.5Khz... 我已附加了这2张图片。 请澄清

第二个查询与先前的查询相同... 根据上面发布的仿真文件、相位噪声为-94、偏移为1K 和10K…… 但实际上、我在10MHz 时测量的是80、参考频率为... 100MHz 时、参考 模拟和实际结果是匹配的.... 在较低的 PFD 下可能会出现什么问题。 请澄清。 我将源的相位噪声和 LMX2595的测量值以及 TICS PRO 设置连接在一起...