Other Parts Discussed in Thread: TLC551, TLV170

主题中讨论的其他器件: TLV170

大家好、

您能否查看下面的查询?

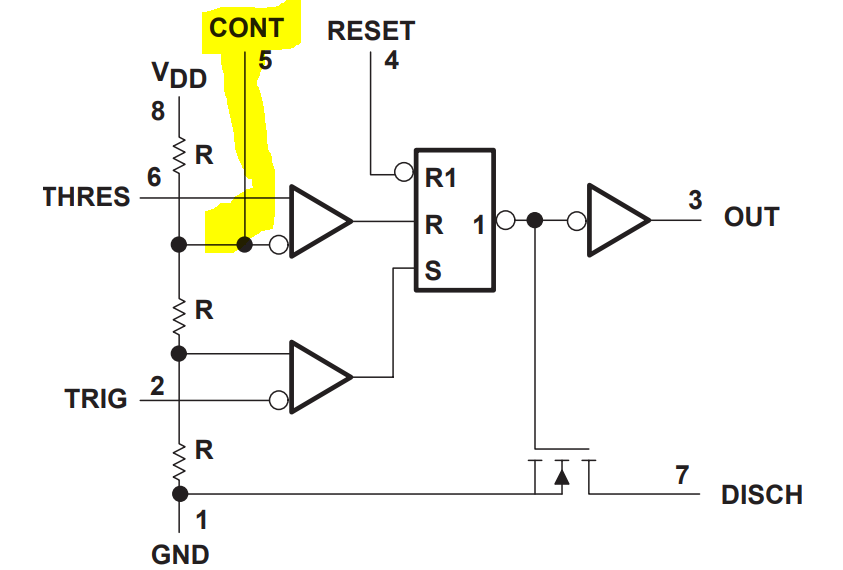

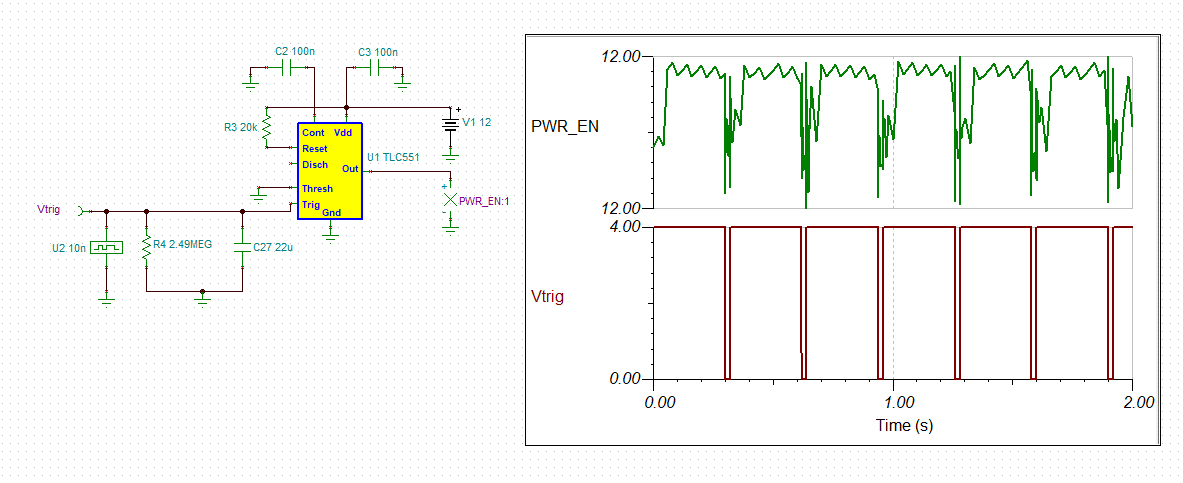

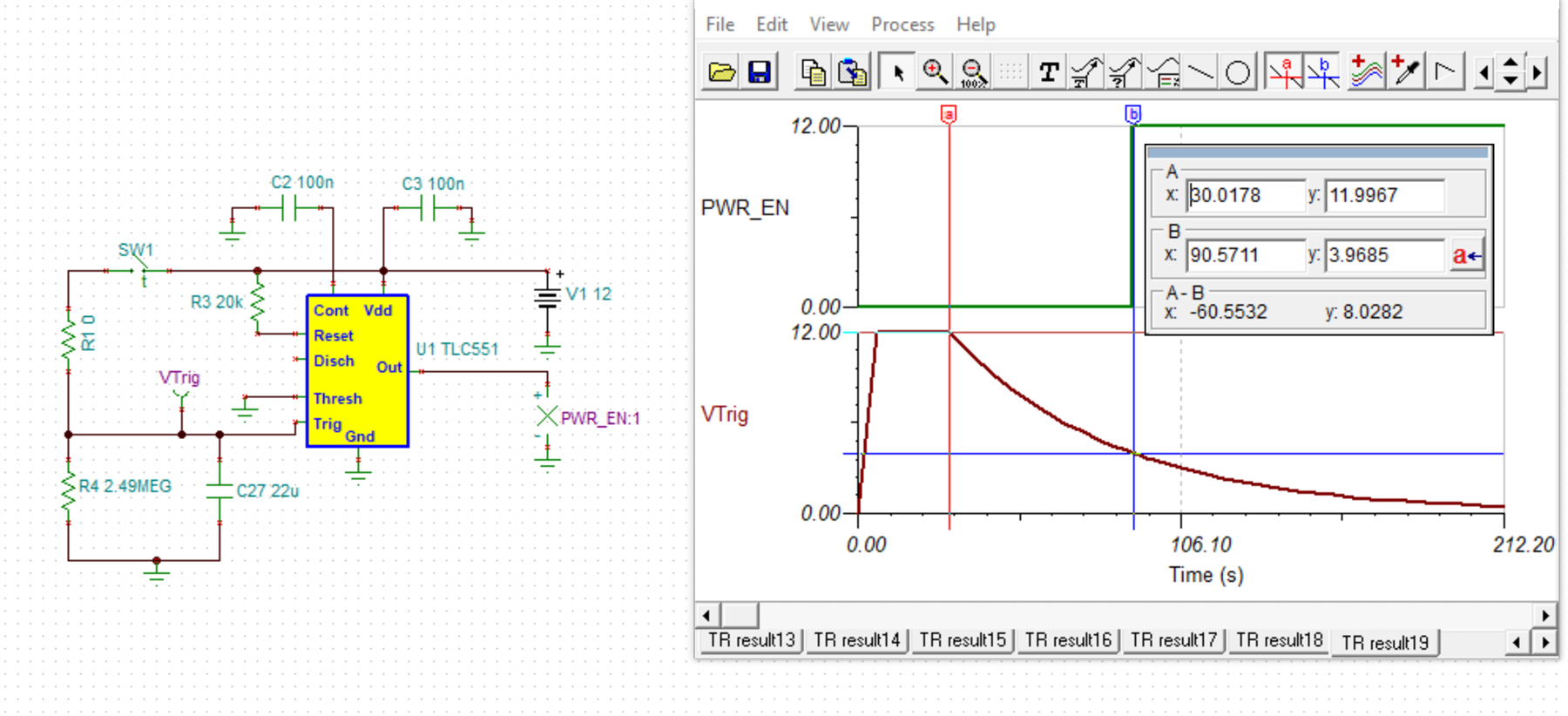

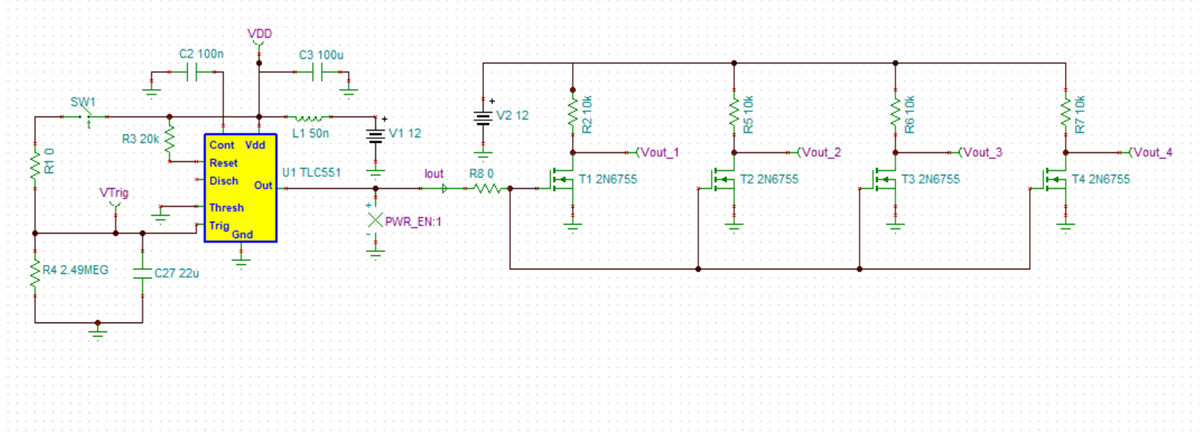

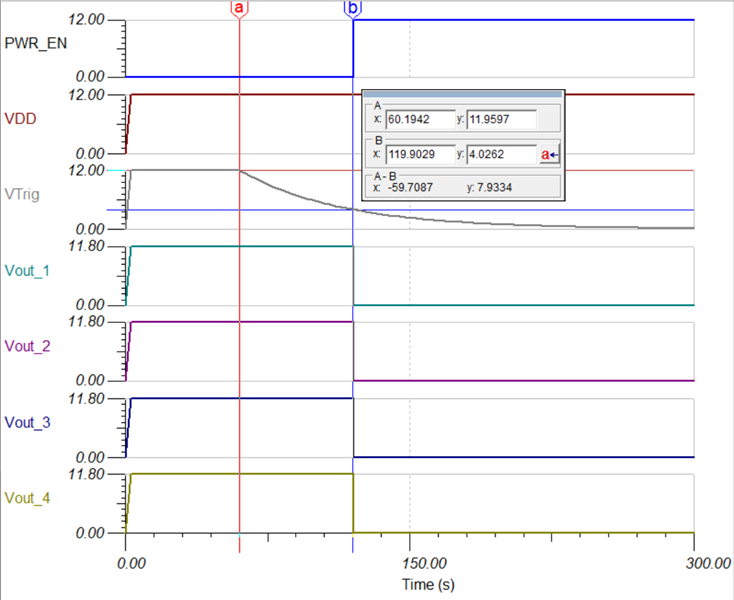

本设计中使用了具有 TLC551CD 芯片的延时时间电路、该电路具有2.49Meg 并联的电容为22uF、连接到 TLC551的触发输入端。 V+为12V、 THRES 连接至 GND、CONT 和 DISCH 引脚悬空。 电容/触发输入高侧的 PMOS 输入最初处于闭合状态(因此电容处于12V)、然后输入打开 PMOS、电容/电容开始消耗。

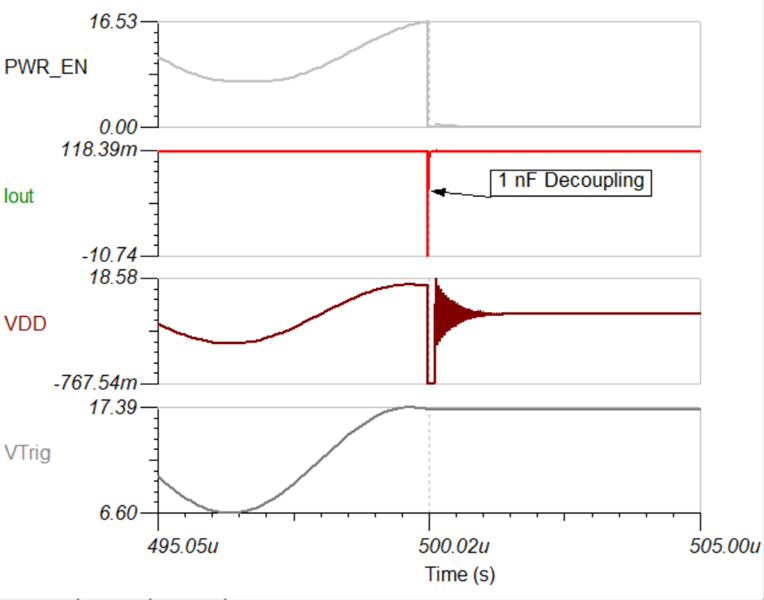

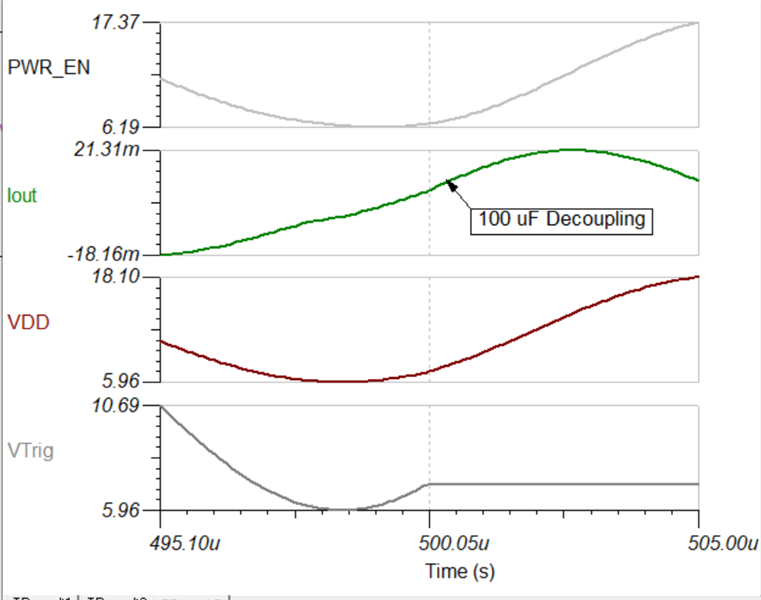

当触发器输入电压达到大约4V (其中551应触发输出发生变化)时、器件将进入振荡状态、此时触发电压将恢复到4.3V、重新漏电到4V 并不停地重复。 551因此不会改变状态。 可以暂时禁用12V、使电容器降至2.5V 范围、然后将其翻转过来、这将触发输出改变状态并保持正常状态。

您能不能帮助解释为什么触发输入电压在此 RC 电路中振荡。 输出翻转时是否需要解决某种电容耦合问题? 在问题期间监控其他引脚时、V+、Cont 或 OUT 上没有振荡。 仅影响触发电压。 客户已验证其他输入没有变化。

如果您需要更多信息、请告诉我。

此致、

Marvin