Other Parts Discussed in Thread: LMX2571

主题中讨论的其他器件:LMX2571

您好!

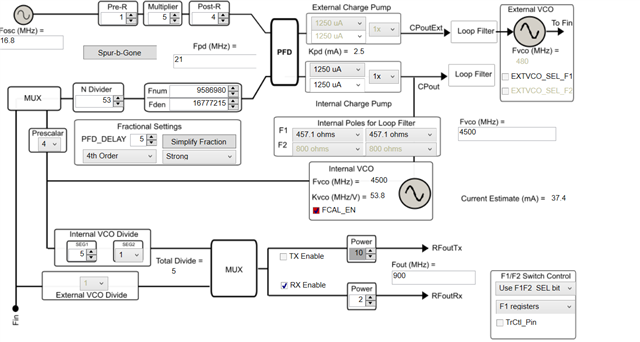

我们的客户正在评估 EVM 上的 LMX2571、然后发现一个奇怪的现象。

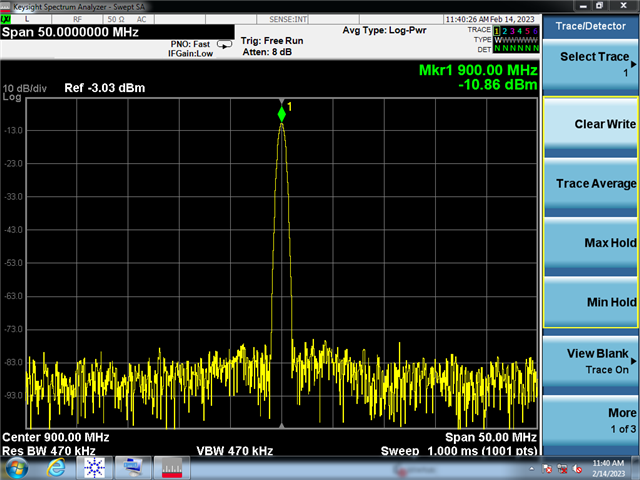

输入16.8MHz TCXO 和输出900MHz。 作为 附加数据、PLL 输出在初始时非常清晰。

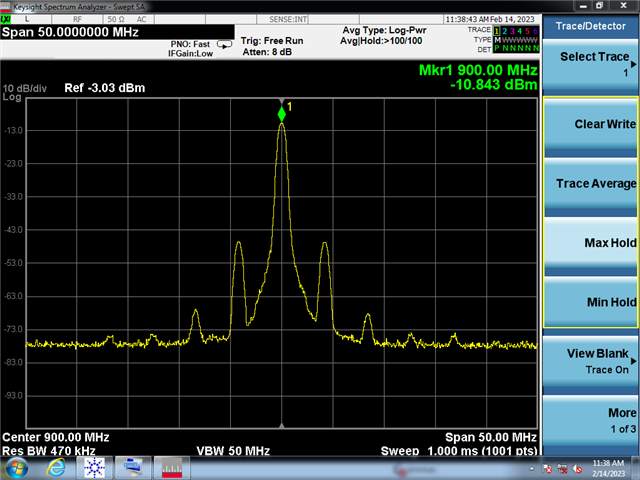

经过一段时间后、大约为4分钟、杂散信号电平在增加。

然后应用初始化、杂散会消失、并在4分钟后重复相同的现象。

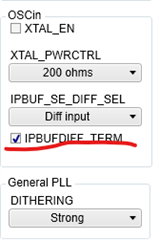

您是否发现寄存器设置有任何问题或任何其他问题?

此致、

Mochizuki

e2e.ti.com/.../2571_5F00_900.tcs