Other Parts Discussed in Thread: LMK01020, CDCLVP1208

您好!

我们目前正在验证一个复杂的时钟分配板 、它采用1个顶级 LMK01020器件来生成8个 LVPECL 时钟、然后使用8个二级 LMK01020器件。 整个设置是可配置的、能够生成多达64个 LVPECL 差动输出时钟。

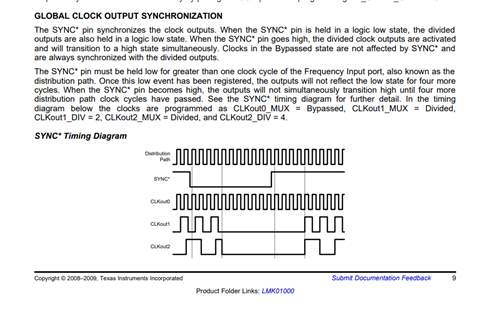

一个关键要求是所有输出时钟必须相位对齐(同步)。 我们在顶层 LMK 器件中置位 SYNC*(低电平有效)、以便对 其8个输出进行相位校准。

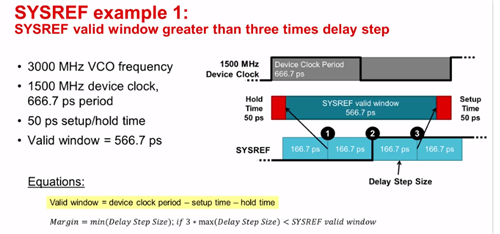

我的理解是,我们还必须在 所有8个二级 LMK 器件中精确地置位 SYNC*(低电平有效),以便同时在所有64个输出中实现相位对齐。 为此, 如《使用多个器件和频率进行 AN-1864相位同步》所示,我们需要保证 SYNC*中的转换尊重相对于分配时钟的设置和保持时间。 我们已搜索这些参数 T-setup-sync-clk 和 T-hold-sync-clk、但 我们在数据表中找不到相关信息。 请提供此规格吗? 或者至少是一个棒球场的价值?

我想设置/保持要求应该在几十 ps 的范围内、因为这是一个非常快的器件。

感谢 您的大力支持、

Jose Jimenez