Other Parts Discussed in Thread: CDCE913

主题中讨论的其他器件:CDCE913

您好、专家、

我有 CDCE913 IC、通过 I2C 进行配置。

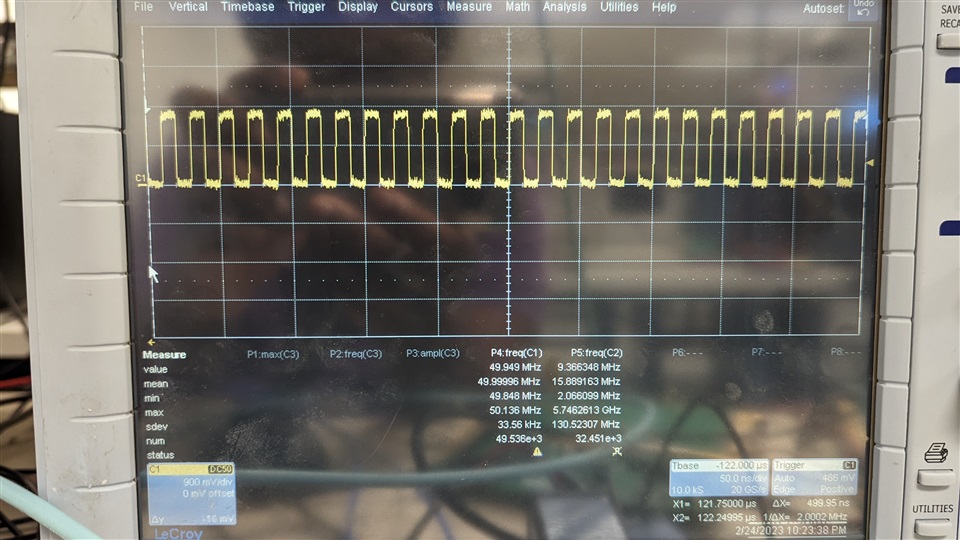

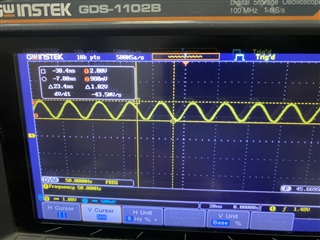

我能够获得所需的输出频率、但当我更改频率时、我的振幅和选择电压会发生变化。 是这样、还是有问题。 用于参考的 PFA 图像。

- 默认25MHz 频率

- 50MHz 频率、具有以下设置

- M=4.

- N=40

- fin = 25MHz

- Fvc0=250MHz

- PDIV=5

- P=1

- Q=20

- R=0

- 配置寄存器为

- 输出选择 Y1_7、FS1_7、SSC1_7和 Y2Y3_7

- Y1_ST1 = 01、Y1_ST0 = 11

- XCSEL = 0x09

- SSC1_7 = 0b0111 / 0b001

- Y2Y3_ST1=01、Y2Y3_st0=11

- SSC1DC = 0/1

- VCO1_0_range = 11 >175MHz

- VCO1_1_RANGE = 11 >175MHz

请帮帮我。

等待您的反馈。

--

谢谢、此致、

Divyesh Patel