主题中讨论的其他器件:LMX2820

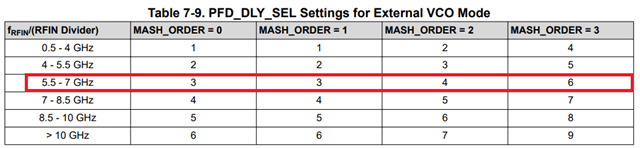

我已使用 HMC1169在外部 VCO 模式下测试用于 LMX2820的评估板、并选择了分数 N。 工作频率为13.125GHz、基准为100MHz (加倍以获得200MHz PFD)、三阶有源环路滤波器、MASH=3。 根据仿真结果、PLL 锁定和相位噪声效果与预期大致相同。 我注意到、边带杂散电平似乎可以通过 MASH 顺序和 PFD-DLY 设置进行管理。 精密泵和滤波器带宽也将得到优化、以帮助实现这一点。

但是、在使用分数 N 操作时、我遇到了我在使用另一个 PLL 器件(ADF4371)时不知道的情况 在观察 LO 信号周围的频谱分析仪(1MHz 跨度、30kHz RBW)时、在没有启用平均值的情况下、我可以看到 PLL 通带内的"移动"杂散。 当接近 LO 信号时、其电平大约为-45dBc。 它与扫描载波频率类似、可能在十分之一秒内通过频带快速传输;它会自行重复、 每隔几秒再次运行一次。 将迹线模式设置为最大值时、很难在显示屏上一致地捕获这些信息、但相关证据很明显。 使用数秒内的最大迹线设置、频谱分析仪显示屏幕将填充高达-45dBc 的波形以及+/-400kHz 范围内的移动杂散包络。

在另一个 PFD_DLY 设置下、杂散电平可以在一定程度上降低。 行进杂散变小、但固定杂散会增加

在整数 N 模式下运行时、移动杂散不出现、因此我认为这是由于某种数值累加而在分数 N 计算中出现的移动拍频。

尝试调整分子、分母、MASH 顺序和 PFD 延迟、但没有明显的方法来消除它。 PFD 延迟设置确实会改变其电平、但代价是 增加普通固定杂散。

我希望这是我错过的一些简单内容、但到目前为止 TI 文档中没有看到这一点。