团队成员:

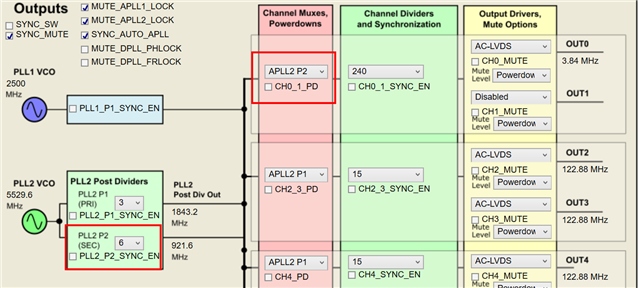

我的客户用带有1.7.2.0版本的 LMK05318B 创建了一些配置文件,它显示了频率计划可以工作 OUT0/1=>3.84Mhz ,所以客户基于这个逻辑并完成 PCB ,但当他们检查 OUT0的 PCBA 时,它变成了 7.68Mhz。

因此、我确认1.7.2.0版本可以通过频率计划、但在实际 PCBA 中输出错误的频率。

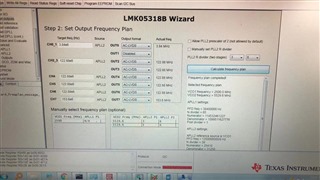

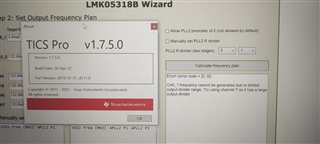

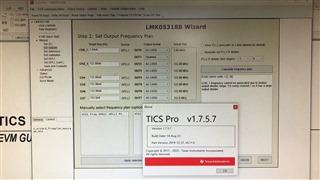

而1.7.5.0和1.7.5.7版本显示以下消息:

错误! (错误代码=[2],0])

由于输出分频器范围受限、因此无法生成 CH0_1频率。 尝试使用通道7、因为它具有大输出分频器

您能否帮助我在客户配置文件之后查看此案例以使其正常工作? ,不同的版本导致不同的结果,它就像一个隐藏的陷阱,如果它不能工作,客户可能需要重新设计 PCBA ,这对他们来说是相当困难的。 又来了!

此处随附了客户配置文件: