在中、我们将尝试将此器件用作单环路 PLL2模式和分配模式、并将 CLKin1用作 REF。

目前仅使用 CLKout0/1、CLKout2/3、CLKout4/5和 CLKout6/7。

1.带 CLKin1的单 PLL2模式

PLL2被锁定并且器件 CLK 输出正常。 但是、没有 SYSREF 输出(请参阅随附的寄存器转储)

2. 采用 CLKin1的分配模式

当 CLKin1为400MHz 时、时钟和 sysref 输出频率均可满足100MHz 和0.1953125MHz (sysref)的要求

不过、当 CLKin1为100MHz 时、频率是不正确的。

这里有一些有趣的事情、

1) 1)时钟和参考频率均除以4 IF 只是更改 CLKin1频率 并且其他设置会保持不变、因此看起来不错

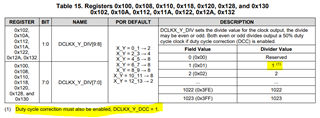

2)如果时钟输出频率设置为100MHz (与 CLKin1相同、则实际测量的频率为33.333MHz。

单个 PLL2和 CLKin1的寄存器转储

e2e.ti.com/.../default_5F00_to_5F00_single_5F00_clkin1_5F00_pll2_5F00_100m_5F00_2m5_5F00_vco0_5F00_2500m_5F00_pll1LD_5F00_to_5F00_pll2LD_5F00_CLKin0_5F00_to_5F00_CLKin1.txt

用于与 CLKin1分配的寄存器转储

e2e.ti.com/.../pll2222b_5F00_0525_5F00_100m_5F00_1m25_5F00_0504.txt