您好!

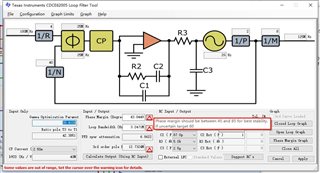

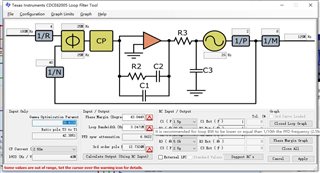

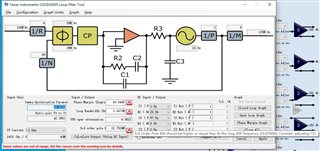

我们的客户将两个 CDCE62005用于级联应用。 但第二个 CDCE62005的某些电路板无法锁定。

他的描述如下:

我们的 电路完全参考了 TI 的官方6678开发板、配置有由 FPGA 控制的 SPI 接口、以及由官方软件生成的配置文件;

我们已经 生产了太多的批卡,但从去年开始失败,去年累计了2个案例,今年迄今又多了7个案例!

锁定故障仅发生在第二阶段;锁定故障发生在第二阶段、通过反转故障电路板的前后芯片。

交换试验排除了芯片问题,非新型板消除了硬件问题和软件问题,交换试验和非批量板卡问题解决了焊接问题,下一个故障排除方法不明确。

请告诉我们问题的可能原因及其解决方案。

此致

kailyn