Other Parts Discussed in Thread: CDCLVC1310

你好

1、原理图检查

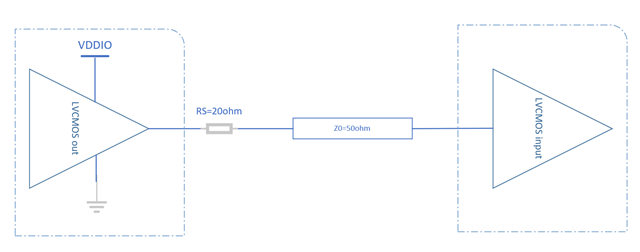

我们将 CDCLVC1310用作 CLK 缓冲器,时钟输入和输出电路如下图所示,请帮助检查电路是否正确。

该电路的详细信息如下:

(1) TCXO VPP = 800mV(±400mV)、削波正弦,频率是76.8MHZ、

(2) 76.8MHZ 是单端 CLK

(3)将76.8MHZ 的削波正弦时钟连接到 PRI_IN

(3)需要将削波后的正弦波转换为 LVCMOS (0~1V8)

2、另外,关于 CDCLVC1310 ,我也有一些问题要咨询建议,

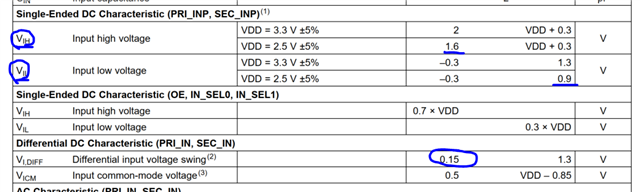

单端直流特征 Min (VIH-VIL)=0.7V,因此芯片的剂量如何达到 WiNG 0.15V。