主题中讨论的其他器件:、 USB2ANY

您好、TI 专家。

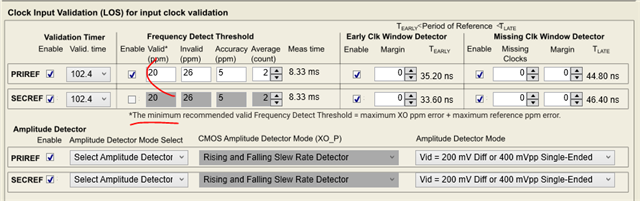

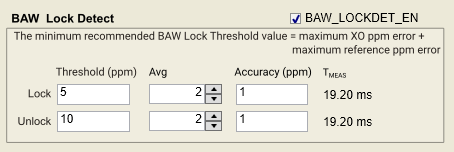

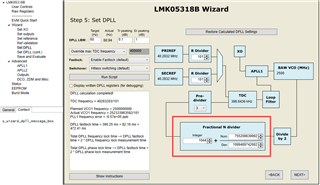

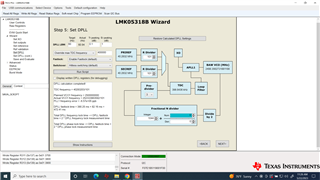

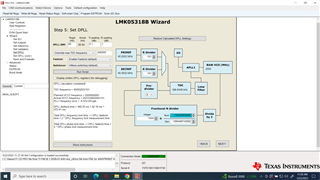

我在电路板上使用的是 LMK05318。 我有20ppm 的频率 DPLL 主基准时钟输入和辅助基准时钟输入的偏差( PRIREF_P PRIREF_N、SECREF_P SECREF_N )。

例如、在我的测试中:

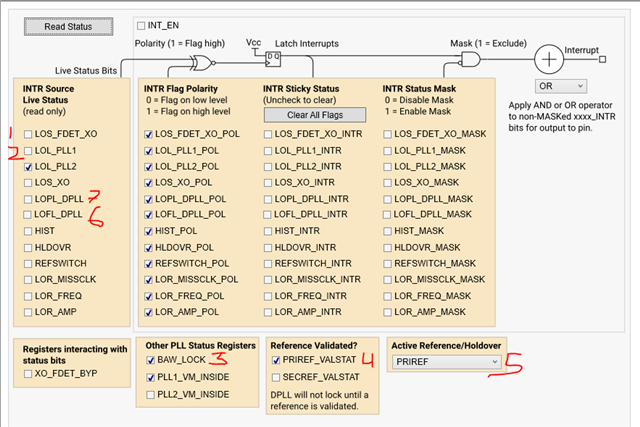

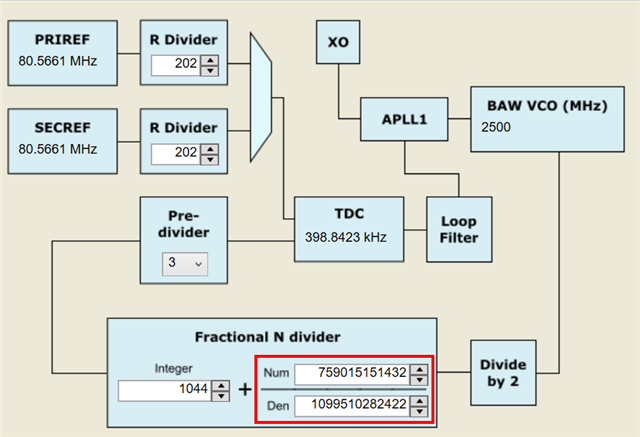

通过 TICS Pro 软件 实现的80566140 Hz 输入使 LMK05318 DPLL 锁定。

通过 TICS Pro 软件实现的80566406 Hz 不会使 LMK05318 DPLL 锁定(LOFL_DPLL=1)、即使 其他设置也是一样的。

80566140 Hz 是基于我们在一块电路板上的实际测量。 80566406 Hz 是我们的计算结果。

什么是频率偏差容差(? PPM) 的主基准时钟输入进行编程? 谢谢!

我无法测量每个电路板来确定 DPLL 主基准时钟输入和次级基准时钟输入的准确频率。

其他条件在我的测试:

XO:48MHz 输入、25ppm。 使用 LMK05318 DPLL 和 APLL1、不使用 APLL2。

谢谢!

法伊森