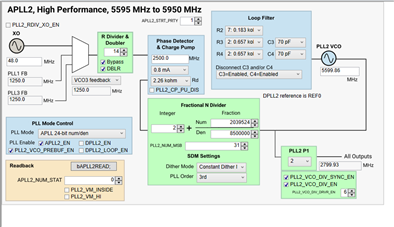

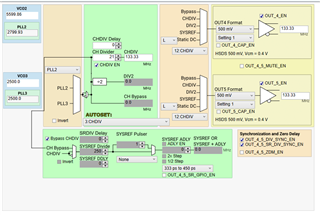

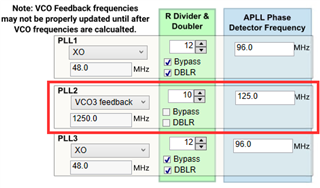

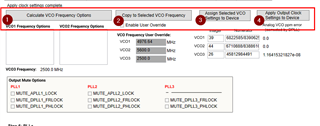

我将尝试使用 LMK5B33216EVM 评估板在输出4、5和6上生成133.33MHz 时钟。 我将使用 BAW 作为其基准的 APLL2。 我将通道分频器设置为21、将 APPL2后分频器设置为2。 计划使用5599.86MHz 的 APLL2频率并将输出除以42以获得133.33MHz。

但是、当我查看通道4的 LVDS 输出时、我得到的频率是138.98MHz、而不是133.33MHz。 这意味着 APLL2运行在138.98 x 42 = 5837.16MHz 而非5599.86MHz。

我曾尝试使用5600MHz 的 APPL2频率、得到了相同的结果。 我还尝试了使用5866.2的 PLL 频率和除以44。 在这种情况下、我得到132.66MHz 的输出频率、这意味着 PLL 以44x 132.66MHz = 5837.04MHz 而不是5866.2MHz 的速度运行。

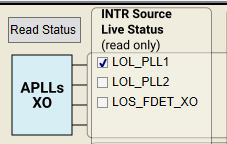

馈入 APLL3的所有时钟都正常工作。 以下是我的配置。 我没有使用 DPLL。 如果有人想查看、我还附加了我的 TiCS PRO 配置。