您好!

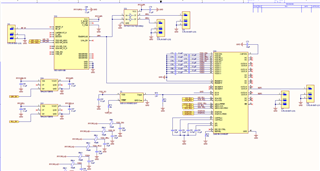

我正在使用 TICSPro 生成原始寄存器、然后我通过 SPI 将其加载到芯片中。 这一切似乎运作良好。 我已将 STATUS0_SEL 设置为"DPPL 失锁(LOFL)"。 该参数设置为高电平、这意味着 DPLL 未被锁定。 我粘贴了原理图、以防任何内容掉线。 我似乎无法插入我的 TICSPro 文件。

我能够在 OUT2和 OUT3上输出10MHz 音调、但似乎未锁定到 GPS 1PPS。 如果有任何事情发生错误、我会很感激您的帮助。

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我正在使用 TICSPro 生成原始寄存器、然后我通过 SPI 将其加载到芯片中。 这一切似乎运作良好。 我已将 STATUS0_SEL 设置为"DPPL 失锁(LOFL)"。 该参数设置为高电平、这意味着 DPLL 未被锁定。 我粘贴了原理图、以防任何内容掉线。 我似乎无法插入我的 TICSPro 文件。

我能够在 OUT2和 OUT3上输出10MHz 音调、但似乎未锁定到 GPS 1PPS。 如果有任何事情发生错误、我会很感激您的帮助。

谢谢!

这是.tcs 文件。 很抱歉我没有提前上传。

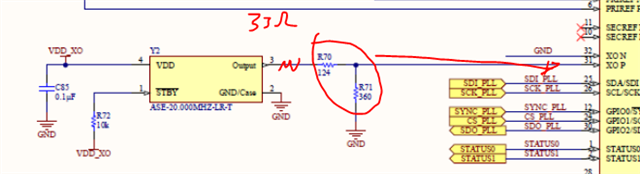

我快速查看了您的原理图-我没有看到任何大问题... 但我建议在输出端放置一个33欧姆的串联电阻器作为 LVCMOS 输出的源端接。 然后将分压器靠近 IC 放置。 我想您具有的距离可能不会导致问题。

——还有你的锁定问题。 您是否尝试使用1-PPS 默认配置?

您的输入是否得到验证?

请注意、应启用1 PPS 相位检测器和验证计时器、所有其他验证均关闭。 输入和 XO 之间的 ppm 误差必须很小、即使是1PPS 相位检测器上的最大63设置也是如此。

73、

蒂莫西

我不知道从1-PPS 默认配置开始是什么意思。

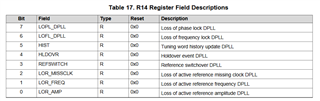

但是、我确实读取了寄存器 R14、R167和 R411。

R14 I 读取以下内容:0xD0。 DPLL 似乎没有从保持事件中退出、因为 DPLL 不会锁定频率或相位。

当我读取寄存器 R167时、我得到了以下命令:0x00

当我读取寄存器 R411时、我得到以下信息:0x00

我不确定如何解释、因为用户编程指南中没有有关这些寄存器的任何信息。

我发送的 tics 文件是否有任何问题?

谢谢。

哈维尔

Javier、您好!

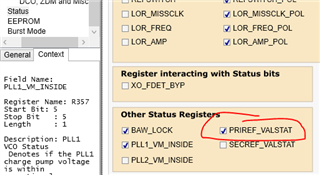

为了详细说明提摩太的评论与参考价值:

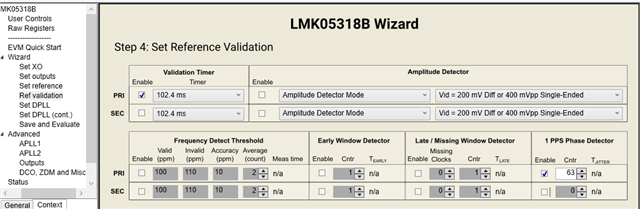

配置1PPS 输入时、仅可启用1PPS 相位检测器和验证计时器进行基准验证。

相位检测器通过 PRIREF_PH_VALID_THR 寄存器设置 XO 精度。 计数器的最大值为63。

如果 XO 超过所需的精度、则将无法检测到1PPS 基准。

您的 XO 的精度是多少? 对于基准进行验证、应小于3ppm。

此致、

珍妮弗

您好!

新的 XO 已经到达。 它是具有±2.5ppm 频率稳定性的12.8MHz。

https://www.digikey.com/en/products/detail/jauch-quartz/O-12-80-JT32C-A-K-3-3-LF/8107804

我更改了.tcs 文件、因为我添加了新的 XO: e2e.ti.com/.../3463.lmk.tcs

I 读取寄存器 R13、R14、R167和 R411以获得以下结果:

R13:0x1D

R14:0xC0

R167:0x2

R411:0x8

要回答您的初始问题、请参考设置如下:

非常感谢您提供任何帮助。

Javier、您好!

请尝试使用此.tcs 文件。 我已经将 OUT2/3设置为10 MHz CMOS。 使用12.8 MHz XO 输入为1-PPS PRIREF 配置 DPLL 设置。

此致、

珍妮弗