主题中讨论的其他器件: LMK04832

大家好、

我想用 LMK04832EVM 有两个时钟,一个是6.25M×另一个是16。6.25M,,两个时钟都有90°PHASE difference.ca,您将向我展示如何配置它。 谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我想用 LMK04832EVM 有两个时钟,一个是6.25M×另一个是16。6.25M,,两个时钟都有90°PHASE difference.ca,您将向我展示如何配置它。 谢谢。

您好、Eric、

只是为了澄清几件事:

1. 16 x 6.25M 是指1个100MHz 输出还是16个额外的6.25 MHz 输出?

2.应使用哪个输出频率作为基准来测量 90°相位差? 例如、6.25MHz 输出是由 90°主导还是反之? 此处的时序图将有助于用作参考。

3.您使用的是内部 VCO 还是外部 CLKIN? 通常很难仅使用90°频率来实现 VCO 相移。 您是指180°、还是确切地说是90°?

获得此信息后、我可以帮助设置配置文件、并在实验中对其进行测试、以确保一切正常。

此致、

康纳

您好、Eric、

有关此器件的 TICS Pro GUI 的更多信息、请参阅 LMK04832 EVM 用户指南: https://www.ti.com/lit/ug/snau215a/snau215a.pdf

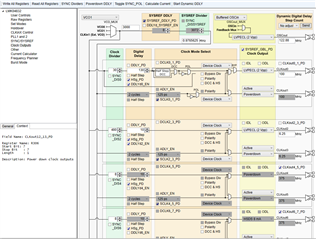

DDLY 代码具有最小值8、最大值1023。 实际延迟测量值等于 DDLY 代码乘以时钟分配频率的周期(可在"时钟输出"页面顶部看到)。

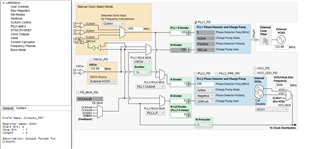

对于此配置、我将使用从 CLKin1 = 200MHz 驱动的 VCO1频率3000 MHz 并关闭 PLL1:

对于6.25MHz 处的90°相移、输出之间的延迟应为40ns。 由于延迟= DDLY 代码/时钟分配 频率:DDLY 代码= 40ns * 3000 MHz = 120。 这意味着、2个输出之间的 DDLY 代码需要相差120、才能之间具有40ns 的延迟。 我将100 MHz 输出的 DDLY 代码设置为130、将6.25 MHz 输出的 DDLY 代码设置为10。

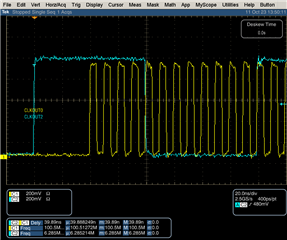

请注意、我没有为此配置使用 SYSREF、因此我可以关闭 SYSREF 块以降低 功耗、但如果您要使用1个时钟输出组(例如 CLKout0/1而不是 CLKout0/2)、也可以使用 SYSREF。 您只需启用 SYSREF、设置延迟、并将输出时钟多路复用器从"器件时钟"更改为"SYSREF"。 以下是我在同步输出后使用此配置文件进行的快速测量:

e2e.ti.com/.../CLKin1-200-MHz_2C00_-VCO1-3000-MHz_2C00_-CLKout0-100-MHz_2C00_-CLKout2-6.25-MHz.tcs

我还附上了 TICS Pro 配置、如果您有任何其他问题、请告诉我。

此致、

康纳

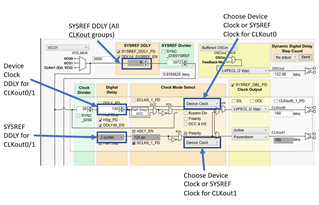

您好、Eric、

如果选择了器件时钟、范围为8-1023的 DDLY 代码适用于 CLKout0和 CLKout1。 如果选择了 SYSREF 时钟、则第二个范围为2-15的框适用于 CLKout0和 CLKout1、并会添加到页面顶部的 SYSREF 延迟。 实际上、器件时钟 DDLY 独立于 SYSREF DDLY 工作。 希望这张图片能让您的幻灯片更加清晰、

此致、

康纳