您好!

我们需要定制 LMX2572通用驱动程序、并且我们在模式 FSK 中观察到一些带有频率偏差的限制。 我们使用评估板 LMX2572EVM。

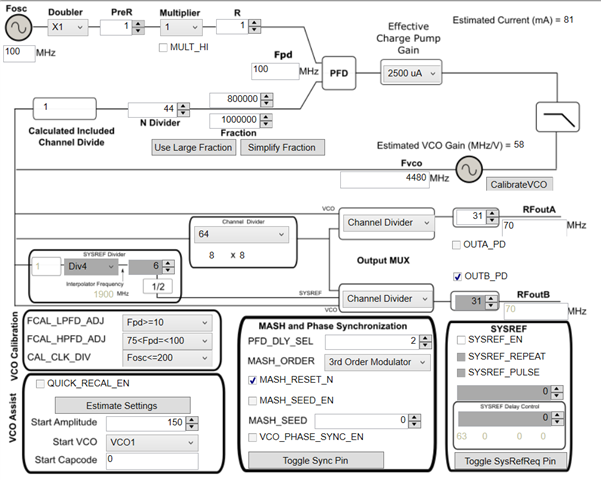

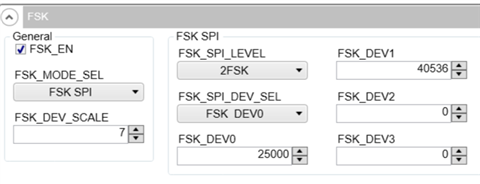

使用 TICS-Pro 可以观察到这些问题。 在测试过程中、我们在"PLL"面板上定义一个固定频率。 然后、我们进入"User Controls"面板的"FSK"部分。 我们按如下方式配置 PLL:

- FSK_MODE_SEL : FSK SPI

- FSK_SPI_LEVEL : 2FSK

- define: FSK_DEV0、FSK_DEV1和 FSK_DEV_SCALE。 9 &10 p73 (FSK_DEV_SCALE 被定义为具有更高的 FSK_DEVx 可能值)。

第一个限制出现:

如果 FPD = 20MHz、并且我们定义了6GHz 的输出频率、则不能出现-20.1MHz 的偏差(从而使输出频率为5.9799GHz)。 +20.1MHz 偏差的计算方式。

或使用相同的配置、我们将输出频率定义为3GHz、最大偏差为3GHz 左右的-10MHz (对应于 Fvco 6GHz 附近的-20MHz 偏差)。 +10.05MHz 偏差的计算方式。

我们似乎不能进行超过 FPD 的负偏差。 当要求 PLL 产生负偏差时、它将仅输出载波频率。

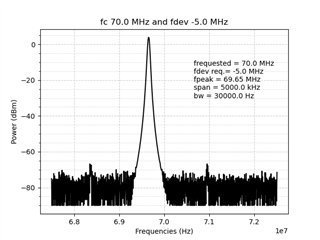

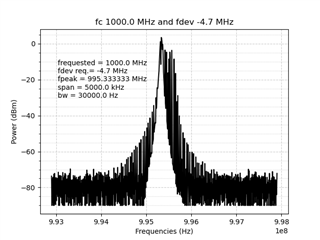

第二个限制也影响了负面偏差。 PLL 输出错误的频率(高于所请求的频率)、并且频谱信号包含大量有害的谐波、如下图所示。

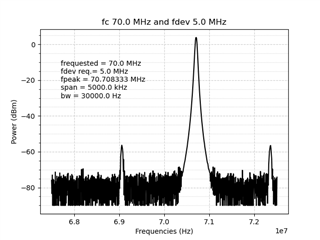

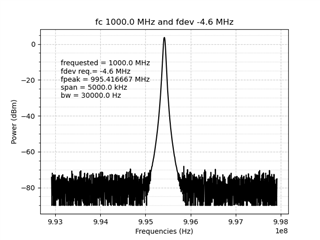

在这里,正常行为:

以下是我们遵守的限制表(此处 PLL_DEN = 100000且 Fosc = FPD = 100MHz):

| 载波频率(MHz) | 最大偏差(MHz) |

| 100 | -0.600 |

| 1000 | -4.6 |

| 2000年 | -9.4 |

| 3000 | -14.4 |

| 4000 | -18.7 |

| 5000 | -25.1 |

| 6000 | -29.0 |

我们观察了不同 Fosc = FPD (20、25、50,100和200MHz)、PLL_DEN (100k、 1M 和10M)或 FSK_DEV_SCALE (最小值或10)。

最大偏差似乎取决于输出频率。 输出频率越低、负偏差就越低。

这种行为是否在某处被描述?

提前感谢您的回答。

此致、

马洛