您好、先生!

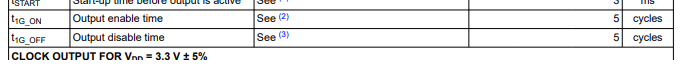

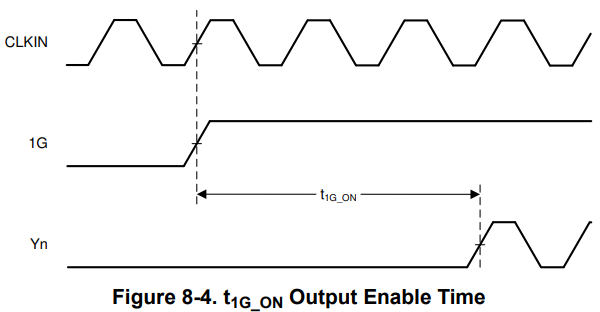

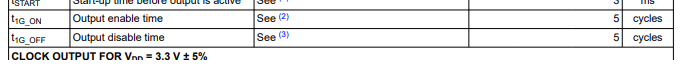

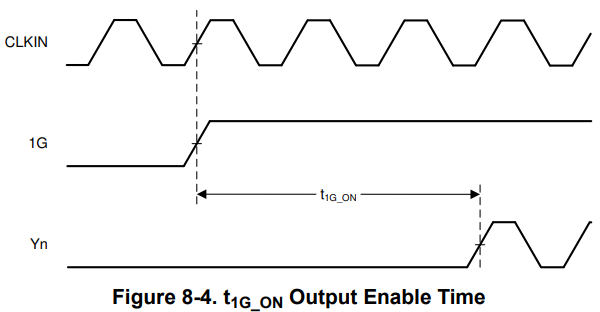

LMK1C1102PWR 的数据表 提到输出需要5个周期的 CLKIN、

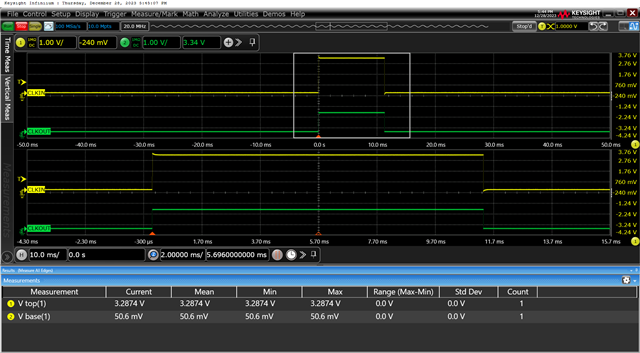

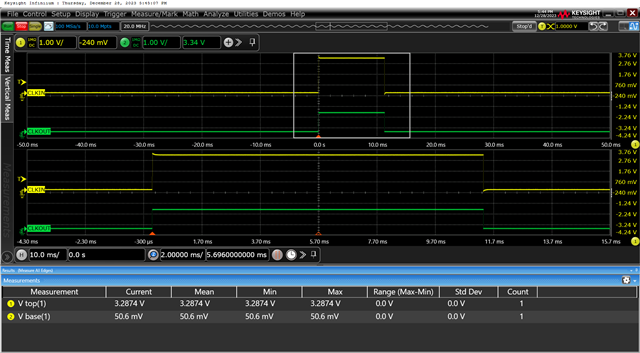

但在我们的应用中、已启用输出仅使用一个周期(如下波形)。

由于目前我们正在调整 FW 行为、因此需要您的意见、以了解是否需要将其调整为5个周期、

或保留一次。 以及此部件的输出使能条件到底是什么、谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、先生!

LMK1C1102PWR 的数据表 提到输出需要5个周期的 CLKIN、

但在我们的应用中、已启用输出仅使用一个周期(如下波形)。

由于目前我们正在调整 FW 行为、因此需要您的意见、以了解是否需要将其调整为5个周期、

或保留一次。 以及此部件的输出使能条件到底是什么、谢谢。

您好、William、

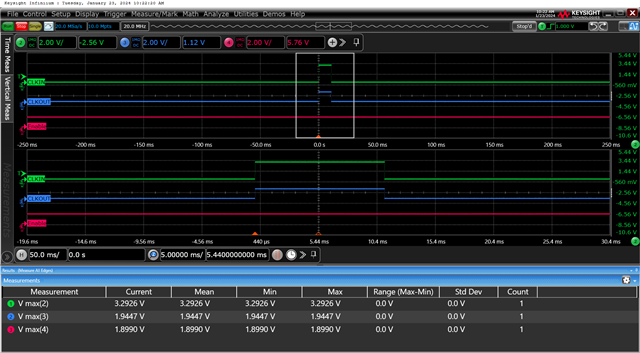

下面的波形就是我们当前的情况、 OE/1G 引脚始终为高电平、

目前、这部分有两个应用(位于两个位置)、

第一个用途是接收一个1信号作为输入。 在这种情况下、输出仅在5个周期后启用是可以接受的。

出于第二种用途、该引脚充当中断、并且只存在一个脉冲。 在这种情况下、我们必须确定此缓冲器是否阻止了中断脉冲。 根据响应情况、如果输入端只有一个脉冲、则可能不会反映在输出中。

作者:William、

第一个用途是接收1个信号作为输入。 在这种情况下,输出仅在5个周期后启用是可以接受的。

正如我们讨论过的、这种情况将起作用、因为时钟输出将在5个或更少周期内。

出于第二个目的,该引脚用作中断,且只存在一个脉冲。 在这种情况下、我们必须确定中断脉冲是否被该缓冲器阻止。

在这种情况下、我在实验室进行了测试、并与我们的设计团队进行了交谈。 OE 通过两个触发器与时钟同步(当 VDD 为低电平时、触发器复位)。 因此、在 OE 通过 VDD 启动时被拉高、然后保持高电平的情况下、仍需要至少2个时钟周期来设置触发器、才能启用输出。 因此、如果您仅在启动时将 OE 拉为高电平、则尝试发送中断脉冲、它将无法正常工作、也无法看到任何输出。 因此、启动时、您需要在中断脉冲之前发送~ 5个时钟周期才能看到输出。

此致、

将会