Other Parts Discussed in Thread: LMX2594, LMX2595, LMX2572, ADC12DJ3200

主题中讨论的其他器件: ADC12DJ3200、LMX2594、LMX2595

尊敬的 TI 团队:

我们正在使用 LMX2572 PLL 为一些快速 TI ADC 计时。

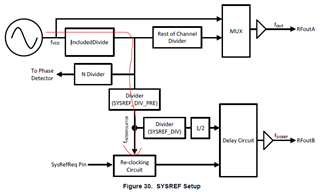

两个 LMX2572位于两个不同的 PCB 上、这些 PCB 提供了输入信号的超低偏斜副本。 这些输入信号在内部首先在每个 PCB 上由一个低速 PLL 进行吸引、这样 SysrefReq 始终在 OSCin 的下降沿发生变化、以便保证在所有条件下都能满足 SysRefReq 引脚的设置/保持时间。

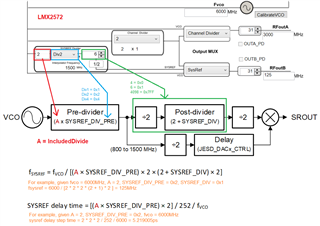

LMX2572处于 SYSCLOCK 重复模式、当前 SYSREF 延迟为0阶跃、配置为在为 ADC12DJ3200计时时合成三种不同的可配置频率2.0、2.5、3.2、或在为 ADC5200RF 计时时合成3.2、4.0或5.0GHz。

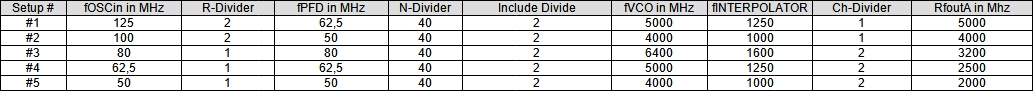

ADC12DJ3200采用以下设置 并向其馈送2.0GHz 时钟、

- f (OSCin)= 50 MHz

- f (SysrefReq)= f (OSCin)/8 = 6.25 MHz

-整数模式(MASH 模式= 0)

- R_DIV = 1

- N_DIV = N'= N / 2 = 40

- include_DIV = 2 (VCO_PHASE_SYNC_EN ="1")

- f (VCO)= 4000 MHz

- f (内插器)= 1000 MHz

- CH_DIV = 2

- OUTA_MUX = CH_DIV

---> RFOutA = 2000 MHz

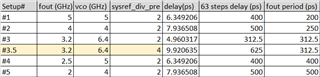

按照数据表"表140. SYSREF 延迟步骤"我观察到(至少对我来说)异常行为。 在使用 SYSREF_DIV_PRE = 2的设置下、数据表中描述的延迟步长约为每步5ps。 我一直在想、为什么 LMX2572的值依赖于分频器、而 LMX2954似乎确实具有9ps 的恒定延迟步长、但嘿。

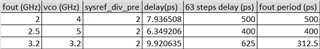

如果步长为一个固定的值(如上面提到的~5ps)、预计在 RefOutA 的一个完整周期内移动 RefOutB (SYSREF)所需的步进数量将会在分别为312,5ps、400ps 或者500ps 的不同周期内有所不同。

但是、当查看 快速示波器上的 RefOutA 和 RefOutB 时、在 RefOutB 上触发、具有三种不同设置3.2/2.5/2.0GHz 的观察结果为:应用不同的 延迟、 在全部三个 RefOutA 速度中、延迟偏移一个 RefOutA 周期(360°)并应用~62步进。

如果所有三个不同频率的步长相同、情况又会怎样呢?

此致

比约恩