您好、团队成员:

下面我对 LMK00105有疑问。 您能在下面回答一下吗?

- 如果我们强制 OSCin 为固定逻辑高电平并且输入 SEL 选择 OSCin、我是否可以预期输出为固定逻辑低电平?

- 该器件是否有 Vdd 和 Vddo 之间的电源序列要求?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Taketo-San:

如果我们强制 OSCin 为固定逻辑高电平并且输入 SEL 选择 OSCin,我是否可以预期输出为固定逻辑低电平?

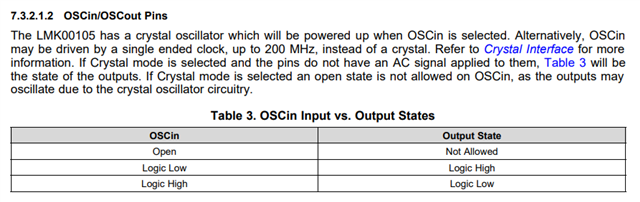

当选择了晶振模式并且没有 AC 信号被施加到 OSCin 时、这个问题是正确的、如数据表第10页中所解释:

user5108279 说:设备是否有 Vdd 和 Vddo 之间的电源序列要求?

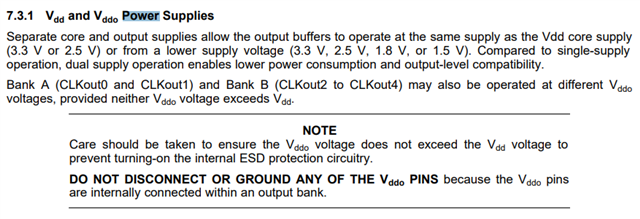

不应存在特定的电源时序。 您是要求仔细检查是否没有一项、还是您在该流程中看到了任何怪异的行为? 此外、如果有兴趣的话、还认为我添加了数据表第9页中有关 Vdd 和 Vddo 的详细信息的快照。 请特别注意以下注意事项:

此致!

安德烈亚

您好 Andrea San:

不好感谢你的评分 抱歉、让我再次询问用于再次检查的电源序列。

因此无论 Vdd 还是 Vddo 是先加电,都不应对 ESD 结构产生影响。

首先为 Vddo 供电、然后它将创造比 Vdd 电压更高的 Vddo 电压条件、直到 Vdd 通电。 通过说明、我假设 Vddo 和 Vdd 之间有保护二极管。 如果出现 Vddo > Vdd+0.3V 的情况、则保护二极管可能会损坏。 我的理解错了吗?

此致、