我在使用 LMK04808。

我想问一下、因为我对 LMK04808的运行有任何疑问。

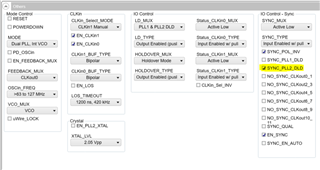

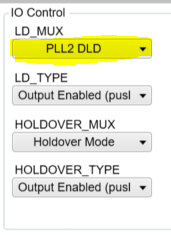

LMK04808配置被用作一个单 PLL 模式配置(PLL2、内部 VCO)。

OSCin 用于 PLL 基准输入。

LMK04808时钟输出0至11的所有12条通道均在使用中。

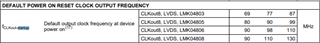

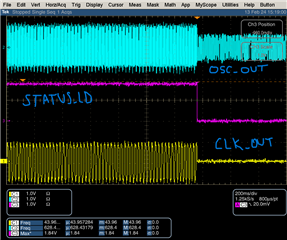

接通 LMK04808电源后、时钟源以设定的值输出。

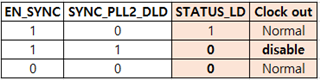

在此状态下、LMK04808时钟输出为正常、即使在没有输入 PLL 基准时钟(OSCin)的情况下(通道6和7除外)。

我知道 Ch6和7不是输出、因为它们是来自 OSCin 的分频类型输出。

除了 Ch6和 CH7、即使在没有输入 PLL 基准时钟(OSCin)的情况下、其余通道也将持续输出。

我想知道为什么时钟输出会继续、即使在 PLL 锁定后 PLL 参考时钟(OSCin)不是输入也是如此。