Other Parts Discussed in Thread: LMK5B33216EVM

您好!

如之前的帖子(e2e.ti.com/.../lmk5b33216evm-tics-pro-settings-not-applied-on-lmk5b33216evm)中所述 、我们拥有 LMK5B33216EVM 板、我们想设计无线同步系统的原型。 我们出于多种原因放弃了这篇文章中描述的1 PPS 器件(我们要在受控系统的 FPGA 上实现它)。

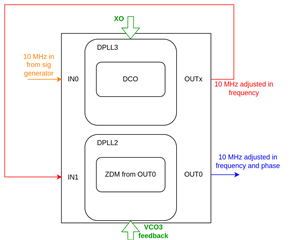

然而、我们仍然感兴趣的是使10 MHz 信号在频率和相位上都受到外部控制、并且具有高精度和稳定性。

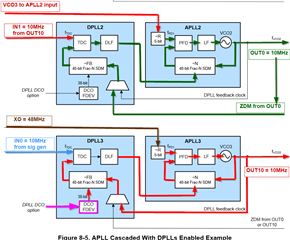

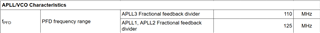

这是我们所想到的想法—— 因为,如果我们理解正确,激活 ZDM 会阻止我们调整频率(既因为输入和输出频率之间的 GCD 不再是输入频率,也因为锁相会阻止输出频率的变化):

在图中、OUTx 是任何输出(我们选择了 OUT4)并反馈到 IN1 (避免这种外部环回将非常好、但我们没有找到在内部环回频率调节信号的方法)。

我们有几个问题:

1.在 TICS Pro 的 IN1字段中、我们已将10 MHz 设置为输入频率、但鉴于频率在 DPLL3动态改变、它将不会是10 MHz (或者、至少不会是10 MHz 上存在的"IN0")。 我们假设此处给定的值仅用于设置不同的 DPLL/APLL 参数、考虑到 DPLL2只需输出与输入频率相同的信号、因此不会出现问题。 是这样吗?

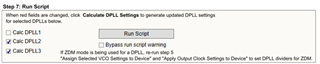

2.我们已经创建了以下配置:

e2e.ti.com/.../desired_5F00_config.tcs

但是主板无法锁定。。。

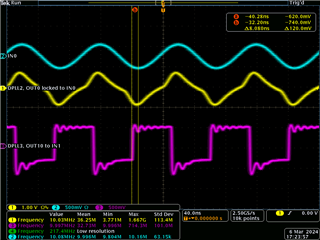

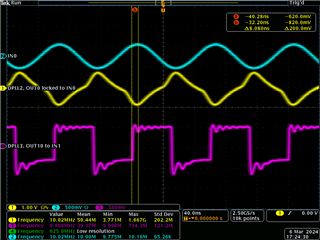

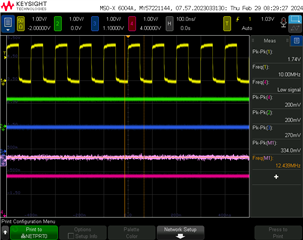

我们可以在示波器上看到以下内容(1:来自信号发生器的10 MHz 输入、2:OUT4_P、3:OUT4_N、M1:数学函数(绿色-蓝色)、4:OUT0):

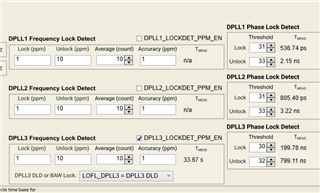

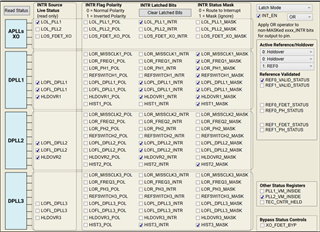

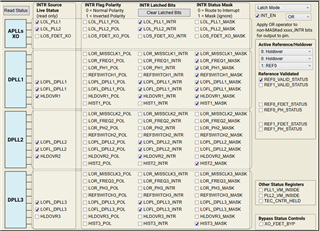

状态提供此信息(确认我们所观察到的内容):

我们的做法有哪些错误?

提前非常感谢、此致、

Rob