您好!

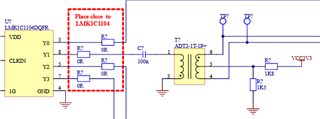

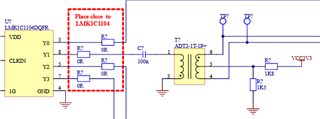

我们要使用平衡-非平衡变压器将 LMK 的其中一个输出转换为差分 LVDS。 是否需要如下面的原理图中那样对缓冲器输出进行交流耦合? 是否有其他意见/建议可实现这一点?

谢谢。

约阿基姆

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们要使用平衡-非平衡变压器将 LMK 的其中一个输出转换为差分 LVDS。 是否需要如下面的原理图中那样对缓冲器输出进行交流耦合? 是否有其他意见/建议可实现这一点?

谢谢。

约阿基姆

Andrea、您好!

感谢您的答复。 我们所使用的 LVDS 接收器通常需要非零共模电压、因此我们要使用电阻分压器将平衡-非平衡变压器的中心抽头偏置到1.2V。 平衡-非平衡变压器是一个纯粹的电路传输器、在我看来、对 LMK 的输出进行交流耦合非常重要、以避免将很大的直流电流驱动到 GND。 LMK 能够提供的输出电流显然存在限制吗?

相关注意事项:LMK 能否从0.2V 摆动到2.8V (使用 VDD = 3.3V)、即使负载为50欧姆? 在50欧姆负载端接至 GND 的情况下保持2.8V 的逻辑高电平、可提供56mA (2.8V/50Ohm)的电流。 在数据表中、对于2.8V 逻辑高电平输出和0.2V 逻辑低电平输出、有1mA 和1mA 的电流注释。 如果电流是限制、则逻辑高电压在端接至50欧姆时只能为50mV。 这是正确的还是我误解了数据表?

总之:当输出端接至 GND 50欧姆时、逻辑高电平和逻辑低电平分别是什么?

谢谢。

约阿基姆

尊敬的 Joakim:

很抱歉响应延迟。 典型的 LVCMOS 接收器为高阻抗、因此 I_OH 和 I_OL 的测试条件列为1 mA。 但是、LMK1C 的输出实际上可以提供比1mA 大得多的电流。 LMK1C 的输出阻抗 约为50欧姆、因此如果它 使用50欧姆负载端接到 GND、由于分压器效应、输出摆幅将减小约一半。 例如、当 VDD = 3.3V 时、如果连接到50 Ω 负载、则 VOH 的最小值约为1.4V。 如果您有任何其他问题、请告诉我。

此致、

康纳