大家好、

每次我从 Tics Pro 配置频率时。 我观察到具有更大1 MHz 失调电压的输出。

您能否指导我如何在 LMX2582芯片组中调整该偏移。

请找到.tcs 文件 e2e.ti.com/.../Tics-pro-files.tcsattached

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

每次我从 Tics Pro 配置频率时。 我观察到具有更大1 MHz 失调电压的输出。

您能否指导我如何在 LMX2582芯片组中调整该偏移。

请找到.tcs 文件 e2e.ti.com/.../Tics-pro-files.tcsattached

尊敬的 Manasa:

我们先看看这个平台。

由于您正在使用 TICS Pro 对板进行编程、因此我们可以消除它是一个软件问题、我们可以将重点放在硬件上。

如果将 MUXout 配置为锁定检测输出、则 MUXout 在编程后输出是否为高电平? 如果 MUXout 为高电平、则 PLL 被锁定。 您看到的漂移可能是由其他原因造成的。 参考时钟是其中一个可能的原因。 您能否提供一张屏幕截图或一段简短的视频来说明漂移是什么样子的?

如果 MUXout 为低电平、PLL 没有被锁定。 在这种情况下、您应该会得到一个非常不同的频率、但在10kHz 量程窗口内不会出现什么。

尊敬的 Noel:

我的另一个观察

当我们给信号发生器的参考频率100MHz 正确锁定 PLL 时. 很明显、PLL 中没有问题。

当我们检查晶体的输出时、我们在晶体输出中观察到8kHz 偏移、

在我们将晶体输出连接到 LMX 后、LMX 的输出无法正确锁定。当我们减小在 LMX 输出中观察到的大约22kHz 偏移范围时、

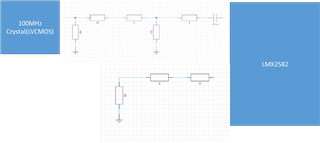

我将附上小视频供您参考。 我们怀疑 LMX 和晶体之间的部件。

还请提出您的想法和建议、

尊敬的 Noel:

是的,我根据您的反馈尝试了修改.

我这边还能观察到晶体 IC 接地没有正确焊接。 在正确焊接后、来自 LMX 的偏移为8kHz、峰值缓慢向中心移动。

请查看下图 LMX 和晶体之间的组件和小型视频、供您参考