大家好!!

我正在使用 LMX2594并想要使用 SYNC 模式。

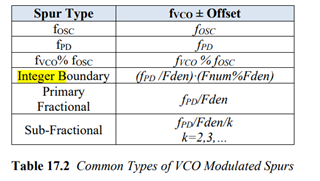

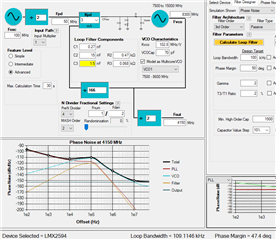

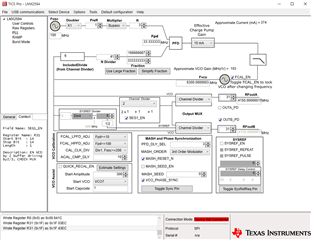

我已将 PLL 设置为以下 pic

有一个问题我想解决。

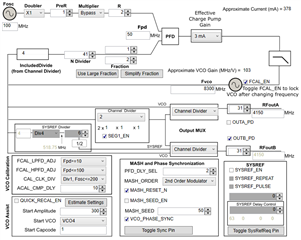

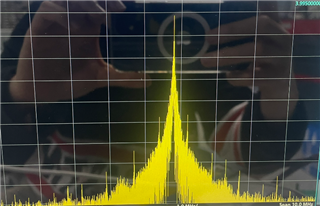

当我设置分数模式、即 PLL 的输出不是 Fosc 的倍数时、

(例如 Fosc:100 MHz,输出:4050Mhz)

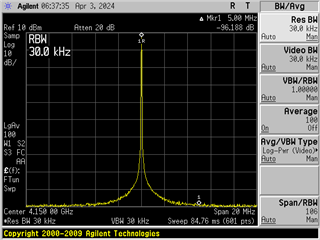

PLL 的输出似乎有一个小数杂散、如下所示:

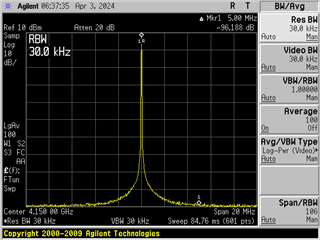

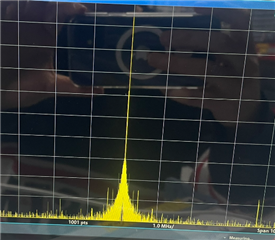

如果我使用整数模式、PLL 的输出是 fosc 的残割方式、则不会发生这种情况。

(例如 Fosc:100 MHz,输出:4000Mhz)

它看起来非常干净、如下所示。

只有在同步模式下才会出现此问题。 (当 VCO_VCO= Phase_Sync 1时)

有人知道这个问题或如何解决?

谢谢