你好

我在 电路板上使用的是 LMK03806BISQE_NOPB 器件。

uWire 可以正常工作;根据数据表中的建议、通过切换 FTEST/LD 进行了测试。

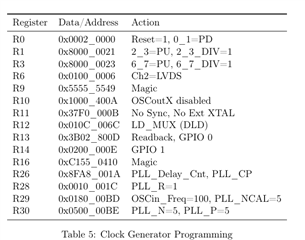

我将按照随附的图加载寄存器。 相关原理图如下所示。

目前我只对 CLK2感兴趣。 其他输出可保持禁用状态。

CLK2上没有输出、此外、引脚33上的 LD 保持低电平。

在这里有什么关于找出故障的想法吗?

感谢您的任何帮助。

大卫

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好

我在 电路板上使用的是 LMK03806BISQE_NOPB 器件。

uWire 可以正常工作;根据数据表中的建议、通过切换 FTEST/LD 进行了测试。

我将按照随附的图加载寄存器。 相关原理图如下所示。

目前我只对 CLK2感兴趣。 其他输出可保持禁用状态。

CLK2上没有输出、此外、引脚33上的 LD 保持低电平。

在这里有什么关于找出故障的想法吗?

感谢您的任何帮助。

大卫

以及更多信息。

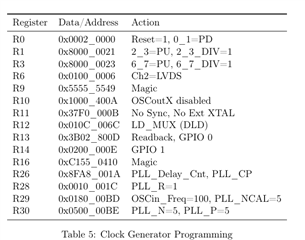

我将编程更改为如下、这导致了以下更改:

LD 引脚现在为高电平。

CLK8和 CLK9上的2.100MHz 输出

3.在其他时钟上仍然没有时钟输出。

请注意、我不对 R4进行编程、CLK8_9的默认上电分频器应为25、但我测得这些时钟的频率为100MHz。

新编程为:

寄存器数据/地址操作

R0 0x0002_0000 复位= 1

R0 0x0000_0060 1_0_DIV=3

R1 0x0000_0021 2_3_DIV=1

R3 0x0000_0023 6_7_DIV=1

R6 0x1111_0006 时钟3、2、1、0=LVDS

R7 0x1111_0007 时钟7、6、5、4=LVDS

R8 0x1111_0008 时钟11、10、9、8=LVDS

R9 0x5555_5549 魔法

R10 0x1655_400A OSCout0启用、div 5

R11 0x37F0_000b 无同步、无外部 XTAL

R12 0x130C_006C LD_MUX (DLD)

R13 0x3B02_800D 回读、GPIO 0

R14 0x0200_000E GPIO 1

R16 0xC155_0410 魔法

R26 0x8F40_0F1A PLL_CP Delay_Cnt、PLL_CP

R28 0x0010_001C PLL_R=1

R29 0x0180_0011BD=100 Cin_Freq、PLL_NCAL=5

R30 0x0500_00BE PLL_N=5、PLL_P=5