请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

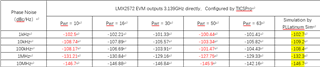

器件型号:LMX2572 R&S FSPN26用于评估 LMX2572评估 板在3.139GHz 下的相位噪声。

结果表明、更改电源配置字将更改相位噪声。 从 pwr = 10到 pwr = 63、最大相位噪声差为7dB。

无论是 VCO 输出还是除以4输出、除以8 输出、它的相位噪声不会随功率变化而变化、只有 VCO 被除以2才会出现这种现象。

我想知道这现象是否正常呢?

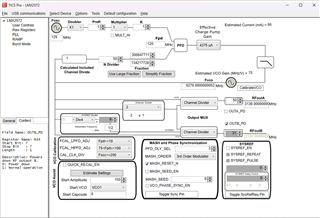

下面是 TICS Pro 设置以及使用不同电源设置测量的相位噪声。