Other Parts Discussed in Thread: LMK00304

当使用 LMK00304芯片输出三个100MHz 差分时钟时、在测量后、所有输出时钟的占空比已达到60%。 这样做的原因是什么? 是否可以通过任何方法将占空比调整为50%?

下面的三个图对应于三个输出时钟。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

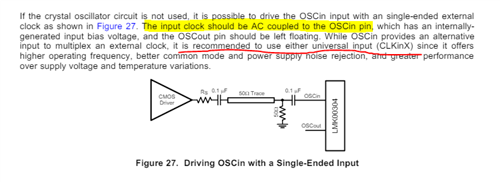

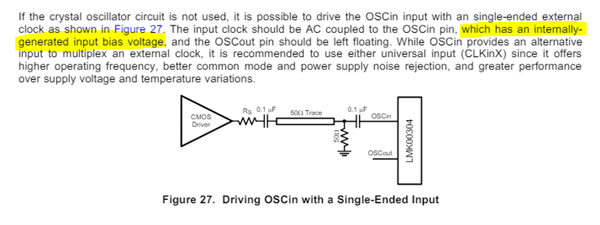

占空比问题可能是由不正确的输入偏置电压引起的、因为客户是直流耦合、应该是交流耦合 。 如 数据表第9.1节所述。

请告诉客户将配置更改为数据表中所示的配置。 此外、为了获得更好的性能、建议对单端输入使用 CLKIN 而不是 OSCin。 有关 CLKIN 单端示例、请参阅数据表第9.1节。

此致、

将会

您好!

在实验室做了一些工作后、我有一些想法。

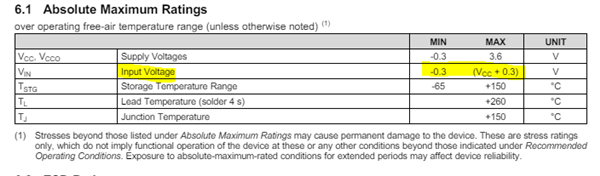

对于您关于第一次测量为什么无法达到50%占空比的第一个问题、这是因为输入信号超出了输入信号的绝对最大值。 OSCin 引脚有~ 0.9V 的内部偏置、因此当施加3.3V 信号时、负摆幅超出输入电压的绝对最小值。 0.9-3.3/2=-0.75. -0.75 <-0.3

考虑到在进行第二次测量时为什么添加50欧姆接地会进一步降低占空比、这是因为您的设计中交流耦合电容器位于50欧姆后面、而在上面显示的数据表建议中、 50欧姆接地端的后方和前方有交流耦合电容。 在50欧姆接地和输入之间需要电容器的原因是 OSCin 引脚弱偏置、因此50欧姆接地将偏置拉至0。

要解决您的问题、请遵循上面的数据表图像中所示的设计。 使用50欧姆电阻器可限制输入过驱/欠驱、使用电容器可防止偏置被拉低。

我希望这对您有所帮助。 如果您有任何进一步的问题、请告诉我。

此致、

将会