主题中讨论的其他器件:LMK5B12204、

工具与软件:

我们在锁定 DPLL 时遇到问题。 在调试期间、我们一直在努力处理可用的文档。 您能说明(并希望更新)文档和软件吗?

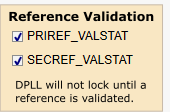

TICS Pro 展示了

和

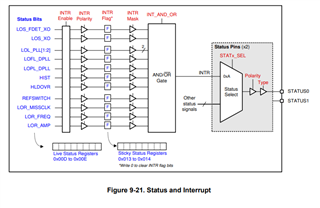

具体详见手册

- 未描述 LOR_MISSCLK

- 所有 LOR_似乎都与 TICS Pro 中的基准验证设置不同。 我已经在 https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1370833/lmk5b12204-non-working-lor_missclk-lor_freq-and-lor_amp-in-tics-pro 上要求您进行阐释

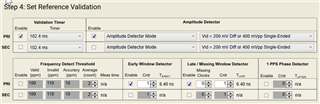

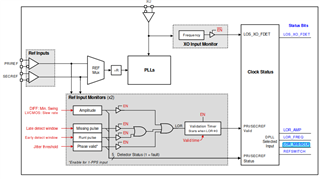

- 方框图中缺少"频率检测阈值"

- 抖动阈值是否是1 PPS 相位检测器?

- 如果信息被"或"删除、Lor_如何工作?

- 如何生成 PRI/SECREF_VALSTAT?

- 手册中没有文档

- LMK5B12204的寄存器说明中缺失

- 添加了 LMK05318B 的寄存器说明 但本指南包含重复和误导性的信息、这些信息已经在多个线程中提到、如 https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1075093/lmk05318b-registers-programming-manual-for-lmk05318b

- 可以禁用"DPLL 频锁检测"。 但未描述相应的寄存器

- 是否 像所有其他检测器一样启用"DPLL 锁相检测"?