工具与软件:

-如果基准返回、则可以从基准振荡器输入(IN_0_P/N)切换到单独的板载振荡器、然后返回、而不会对输出时钟产生干扰。 我不确定自动反向和/或手动保持模式是否适用于此情况

-CAN 输出 LVDS 1.8V 和 LVCMOS 1.8V。 我看到这些参考设计、但我的担心是、在将 LDO 放在电路板上之前必须在器件上进行编程、以避免损坏下游器件

-禁用 PLL 消耗的电流很小或没有电流,因为我们已经超过了我们的最大功率要求。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

-如果基准返回、则可以从基准振荡器输入(IN_0_P/N)切换到单独的板载振荡器、然后返回、而不会对输出时钟产生干扰。 我不确定自动反向和/或手动保持模式是否适用于此情况

-CAN 输出 LVDS 1.8V 和 LVCMOS 1.8V。 我看到这些参考设计、但我的担心是、在将 LDO 放在电路板上之前必须在器件上进行编程、以避免损坏下游器件

-禁用 PLL 消耗的电流很小或没有电流,因为我们已经超过了我们的最大功率要求。

大家好、Lucas:

LMK5B33216支持在保持(XO 输入)和 DPLL 基准输入(INx)之间进行无毛刺切换。

两种模式都提供无干扰切换。 您可以选择最适合您的系统需求的模式。 手动保持是在可用时手动选择要使用的 INx。 自动反向允许器件自动选择要使用的 INx。 如果 INx 不可用、则器件在两种情况下都会在无干扰的情况下自动切换到保持模式。

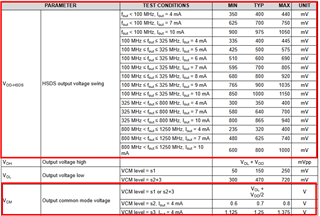

2. 1.8V LVDS 的共模和摆幅是多少? LMK5B33216支持可编程摆幅和共模、可连接多种输出类型。 1.8V CMOS 寄存器通过寄存器设置进行配置、并且仅在 OUT0和 OUT1上可用。 您可以选择 ROM 第3页来启动具有禁用输出的器件、然后根据需要配置输出。

此致、

Jennifer

不过、我们对所有这些时钟输出进行交流耦合、很肯定以上内容没有实际意义

-差分摆幅:0.6≤VREFIN-DIFF≤1.7V

至于使用 ROM 第3页来禁用所有输出、这在一定程度上是我的预期。 因此在我们最后、我们需要找到一种在将这些信号馈送到下游 FPGA/处理器以避免损坏任何器件之前进行编程的方法

进一步探究 LMK5B33216、对我们的应用而言、它似乎消耗了太多的功率、这让我重新考虑使用该部件。 我们是否有类似的东西具有更低的功耗?