Other Parts Discussed in Thread: SN65DSI83-Q1, CDCEL913, SN65DSI83, CDCE913

主题中讨论的其他器件:SN65DSI83-Q1、 SN65DSI83、 CDCE913

工具与软件:

尊敬的专家:

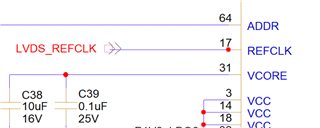

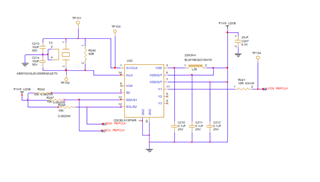

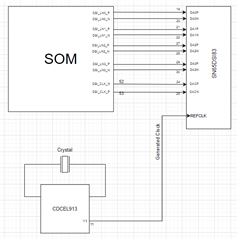

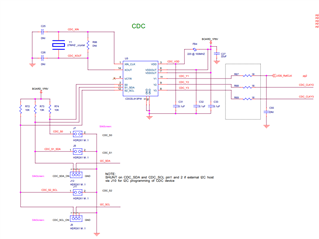

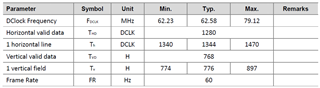

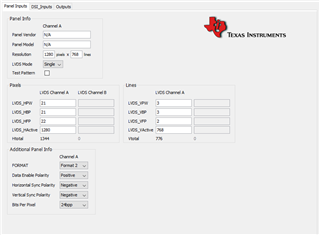

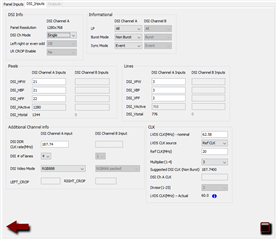

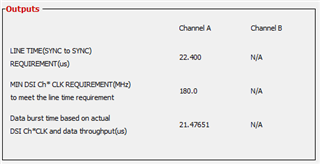

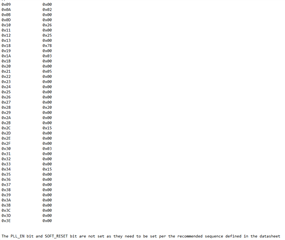

我们目前正在将 SN65DSI83-Q1用作我们的 LVDS 转换器。 不过、我们遇到了 SOM 生成的时钟信号中的噪声和抖动问题。 为了解决这一问题、我们决定将 CDCEL913时钟发生器用作外部参考时钟。 随附的是时钟发生器的方框图和原理图。

您能否告知 LVDS_REFCLK 是否需要上拉电阻器? 此外、我们的设计是否需要进行任何其他修改?

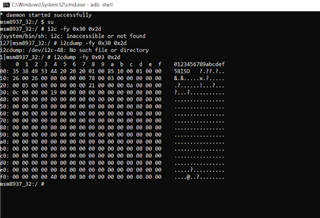

我们还会在 SN65DSI83中遇到 PLL 解锁消息、其导致输出关闭。

谢谢!

Adarsh Verma