工具与软件:

尊敬的 TI 专家:

我正在使用 BQ32002D RTC IC、但从备用电源获取的电流为74.4uA、这远高于数据表中所述的电流。

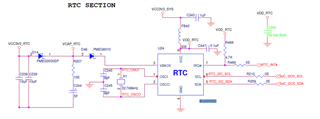

下面是我的同一电路原理图。 如果原理图有任何问题、敬请告知。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 TI 专家:

我正在使用 BQ32002D RTC IC、但从备用电源获取的电流为74.4uA、这远高于数据表中所述的电流。

下面是我的同一电路原理图。 如果原理图有任何问题、敬请告知。

尊敬的 Noel:

在本例中、当我们在断电后向 VCC 施加 Vback 时、将会持续施加 RTC [3.3V]。

但我们不会为 VCC 提供任何脉冲、而是直接施加来自系统3.3V 电源的3.3V 电压。 因此、当电路板开启且电路板关闭时、VCC [3.3V]始终可用、然后使用超级电容器[3V 和5F]施加 VBACK=3.0V。 现在、在该电路中、我们已经观察到了下面的点、

1.当电路板开启并应用[3.3V]时、在本例中、Vback 功耗为0mA、但当电路板断电且未应用 VCC [VBACK=0V]时、VCC 在大约50秒内的初始几秒内功耗较低、1.9uA - 2.1uA、在这几秒后、VCC 电流消耗增加30uA。 您能解释一下为什么这个电流会增加以及如何解决这个问题吗?

让我们知道 VCC 引脚上的1ms 脉冲是强制性的吗? 如果我们只是通常在电路板上电后持续施加此 VCC [3.3V]、会怎么样?