Other Parts Discussed in Thread: LMK04828

工具与软件:

尊敬的专家:

对于同步多个 LMK 器件、我仍然有一些问题。 当我在两块时钟板上测试 LMK 的500MHz 输出时、我注意到它们之间存在一些抖动、这也影响了 LMX 输出。

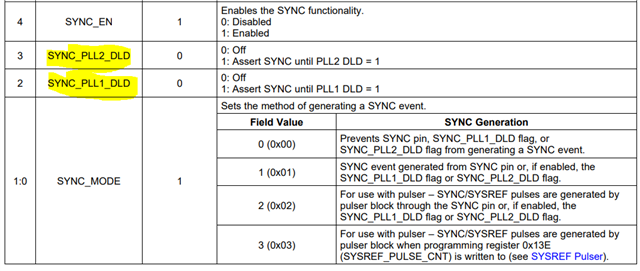

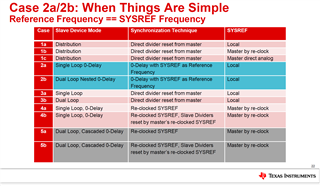

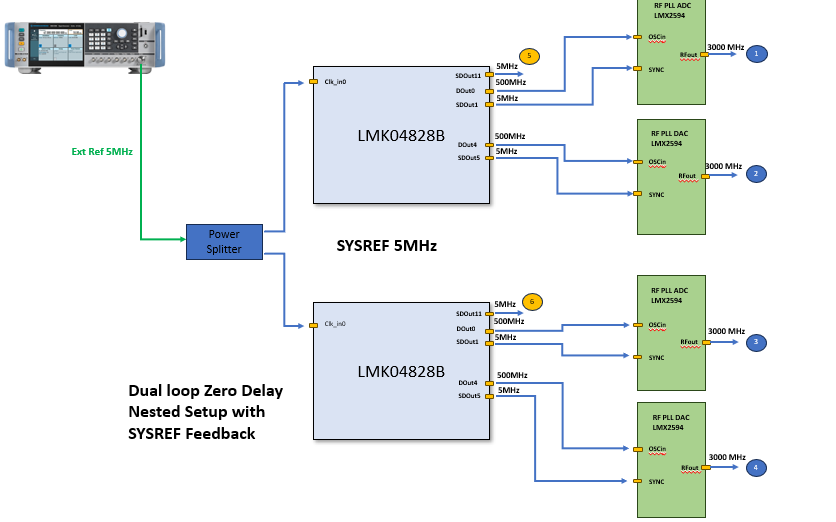

我的当前配置基于图中所示的2b 情况(双环路嵌套 ZDM)。 我认为对于 ZDM、500MHz 边缘 输出应与5MHz 输入的边缘对齐。 如果两个5MHz 边沿对齐、则两个500MHz 边沿都应对齐。 我当前使用 clkin0作为5MHz 基准输入、我是否仍需要向 SYNC 引脚发送同步脉冲来复位分频器? 您能向我指出正确的方向吗?

谢谢!

LMK04828时钟文件:

此致、

Jingda