Other Parts Discussed in Thread: LMK1C1103, LMK1C1104, LMK1C1102

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK1C1103 主题中讨论的其他器件:LMK1C1102、 LMK1C1104、

工具与软件:

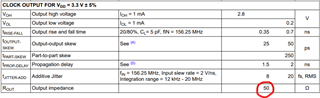

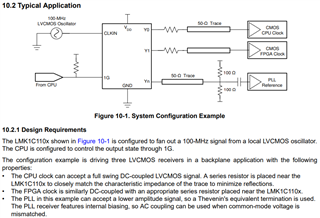

LMK1C1102/LMK1C1103/LMK1C1104的输出阻抗 如 第7.5节所示。 这会随电压的变化而变化(Ro = 50Ω@ 3.3V、Ro = 52.5Ω@ 2.5V、Ro = 60 @ 1.8V)、但稍后在数据表的10.2节"典型应用"中显示了通过串联端接与50Ω 传输线的匹配、并表示"一个串联电阻放置在 IC 附近、以与布线的特性阻抗密切匹配、从而最大限度地减少反射"。 如果缓冲器的输出阻抗已经是50Ω、则匹配50Ω 传输线肯定不需要额外的显式串联电阻器。 该典型应用是否错误?如果是、那么缓冲器的实际输出源阻抗是多少?