Other Parts Discussed in Thread: LMX2594, LMX2572, LMX2582

主题中讨论的其他器件:LMX2594、 LMX2572、 LMX2582

工具与软件:

您能给我一些附件吗?

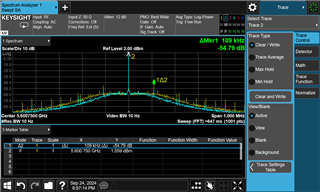

我已在图1 (图2)中检查了 LMX2594的 FPD 和 Fout。

因此、我们在图3 (黄色)中确认了波形。

您能猜出 Δ109kHz 杂散是由什么产生的吗?

此致、

横内昭彦

图1.

图2.

图3.

图3.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Noel、您好

感谢您的建议。

杂散 Δ Q 由 Fosc (Δ109kHz)引起。

目前、我们正在考虑在5.6G 频带内锁定250 kHz 阶跃或500 kHz 阶跃的 PLL。

除了 LMX2594之外、是否还有其他合适的器件?

或者、如果我们使用 LMX2594、我们是否有任何可以通过设置 Fosc 和 FPD 来抑制杂散的频率?

顺便说一下、我们考虑环路带宽约为100kHz、相位噪声积分值为-40dBc/Hz (100Hz 至200kHz)。

此致、

横内昭彦

尊敬的 Yokouchi-san:

我们有 LMX2572、它可支持高达6.4GHz 的频率、是一个低功耗合成器、但相位噪声不如 LMX2594。

无论它是小数通道、都有可能出现小数杂散。 使用我们的仿真工具 PLL Sim (https://www.ti.com/tool/PLLATINUMSIM-SW)可预测杂散频率。

如果我们使用窄环路带宽、则可以降低分数杂散。 不过、设计目标是最佳抖动、因此必须使用宽环路带宽。

小电荷泵电流可以减少杂散、但同样、较小的电荷泵电流将限制可能的最大环路带宽。

我们可以尝试的另一个窍门是对 PLL_DEN 使用非理性的数字。 例如、我们可以尝试2400001、而不是使用240。 杂散应更低、但相位噪声可能会增加。

您可以查看 LMX2582数据表第8.1.1节。 简化规则。