Other Parts Discussed in Thread: LMK04828, AFE7950, AFE7950EVM

主题中讨论的其他器件: AFE7950、 AFE7950EVM

工具与软件:

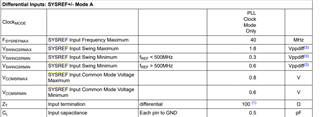

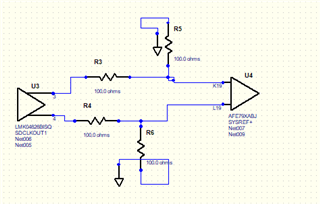

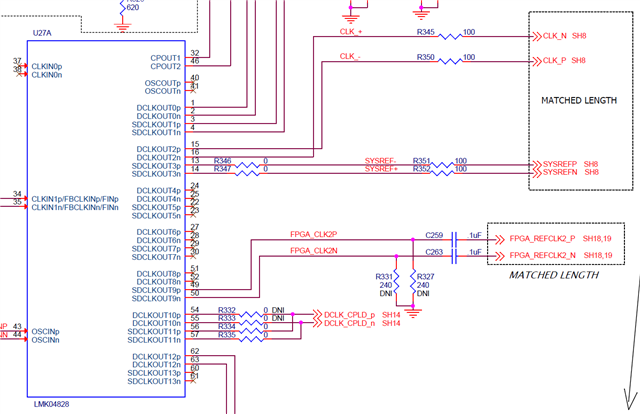

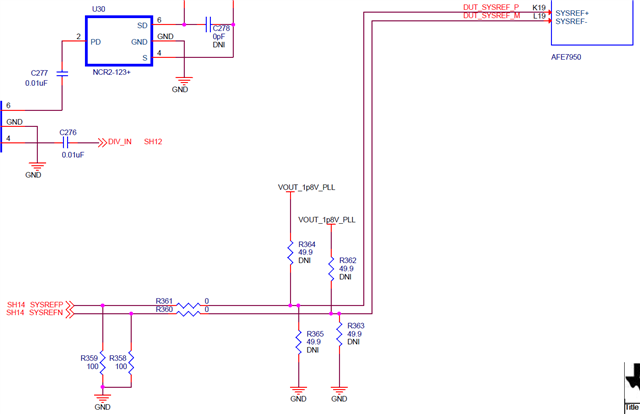

我正在查看 AFE7950EVM 参考设计、有一个从 LMK04828传输到 AFE7950的 SDCLKOUT3差分时钟信号。 信号依次通过串联的100欧姆电阻器和100欧姆接地电阻器、然后到达 AFE7950 SYSREF 输入上的100欧姆差分电阻器。

此终止方案可能是为了将 LMK04828的输出保持在 AFE7950允许的电压范围内。

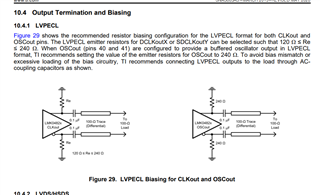

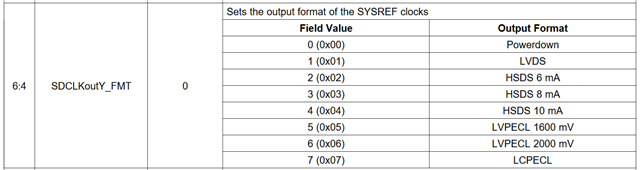

给定 SDCLK 输出的格式选项和所选的终端时、输出可能是 LVPECL。

我对输出格式的假设是否正确? 如果是、如何计算驱动器输出端的共模电压? 端接电阻分布在时钟和收发器原理图页面中。 它们应放置在相对于驱动器和接收器芯片的布局中的什么位置?