工具与软件:

您好!

在 LMX1214EVM 中、所有 PU 和 PD 电阻值均为10K 0402 63mw。 在数据表表表表7中、在使用1K 时、CLKx_EN 将连接至 VCC。 10K PU 至 VCC 是否可接受?

2. DIVSEL、MUXSEL 的 PU 和 PD 电阻是否可以为10K?

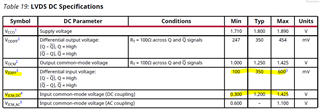

3.在未使用 CLKOUT 的情况下、为了终止它、我们保留100nF 的交流电容和50欧姆的 PD。 80mW 是否足以满足50欧姆要求?

CLK 缓冲器输入为1800MHz、而 CLKOUT 为225MHz LVDS 到 FPGA。 AC-CAP 当前设置为100nF。 这种行为合适吗? 或者您会建议 pF 范围内有任何值吗?

谢谢