工具与软件:

您好!

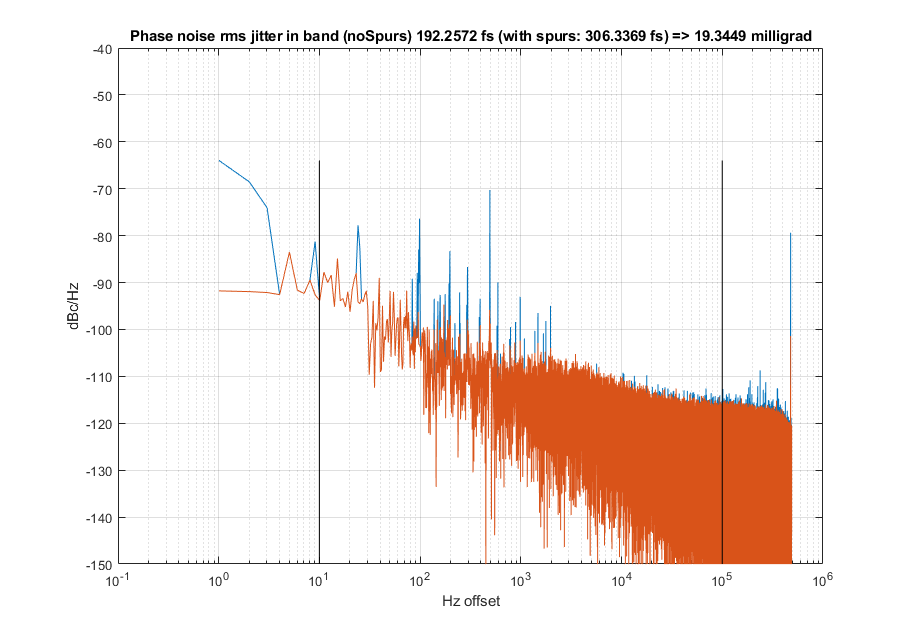

APLL3/DPLL3输出中的相位噪声杂散存在一些问题。 只有 APLL3处于活动状态时、输出相位噪声很好、但是、当我们启用 DPLL3时、我们会在50Hz - 1000Hz 偏移频带内收到一些明显的相位噪声杂散。 由于杂散、启用 DPLL 时产生的额外相位噪声约为~250fs rms。

我们的设置为:f_VCO = 25MHz、f_ref = 10 MHz、DPLL_BW = 1Hz、f_TDC = 1 MHz、f_OUT = VCO3/4 = 614.4MHz (不同的 DPLL_BW 和 f_TDC 产生相似的结果、杂散频率和振幅略有不同)

我们使用 TICSPro 来计算寄存器值。

这是预期行为吗? 或者、我们如何缓解该问题呢? 对我们来说、10Hz 至100kHz 的偏移频带非常重要。

非常感谢您提供的任何帮助和建议、

Christoph