Other Parts Discussed in Thread: LMK04208

工具与软件:

您好!

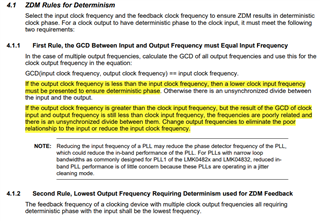

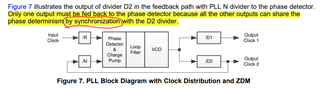

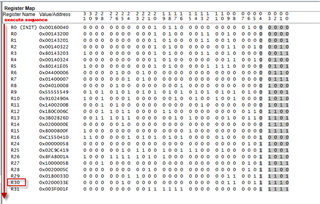

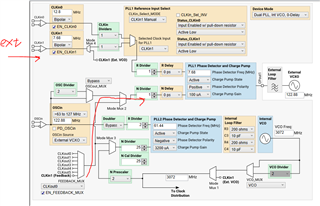

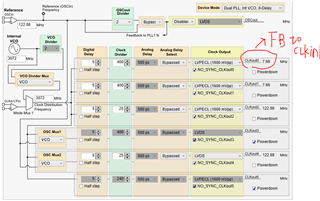

我希望 LMK04208在电路板上的双 PLL、内部 VCO、0延迟模式下工作。 它将在 内部路径中将 CLKout0反馈到 PLL1、如下图所示。 时钟设置 如下所示:

CLKin1:来自信号发生器的外部7.68MHz 正弦时钟

CLKout0:7.68MHz

CLKout1:7.68MHz

CLKout2:122.88MHz

CLKout4:122.88MHz

使用 示波器进行测试、我发现 CLKout0和 CLKout1无法对齐、并且 在下电上电期间没有固定相位关系。 我认为该时钟计划或设置完全符合零延迟模式的两条规则。 但 CLKout1无法与 CLKout0相比与 CLKin1共享相同的相位关系、这是为什么?

附加.tcs 文件以进行 检查。

提前感谢!

此致!

Jason