Other Parts Discussed in Thread: CDCE6214, LMK03328, LMK04832

主题中讨论的其他器件: LMK03328、 LMK04832

工具与软件:

代表客户:

选择 PFD 频率、环路滤波器设置等的指导原则是什么... 相位噪声、才能实现尽可能低的相位噪声?

我在 E2E 上读到、环路 BW 越多越好?

谢谢、-Steve

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Steve、

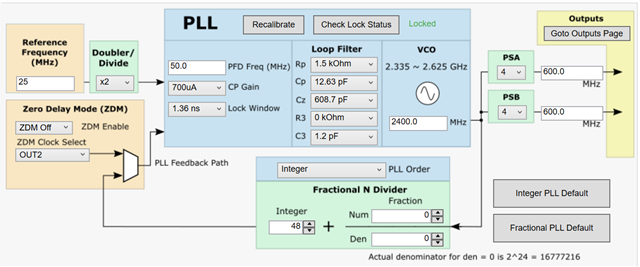

我发现、将 CP 增益降低到700uA 并将 PLL 更改为整数模式[请参阅下文]可提高抖动性能、但与您的电流配置相比、抖动性能不会显著提高。

关于该器件、我想注意以下几点:

虽然 CDCE6214具有低 附加 抖动、但它不一定是抖动清除器。 如本 应用手册中所述、清除抖动需要窄 PLL 带宽。 在本例中、"窄"频率低于10kHz、具体取决于所需的性能。 例如、LMK04832 (双 PLL 抖动清除器)的最小带宽为10Hz。 可用作抖动清除器的 LMK03328时钟发生器的最小带宽为200Hz。

CDCE6214的最小带宽为 100kHz . 本质上、虽然 CDCE6214可以高效地使用已清理的输入基准、但它无法很好地清除噪声输入基准。 这就是为什么该器件在数据表中被描述为"中等级别抖动"-它在输入基准具有低抖动时表现良好、但如果输入端有太多噪声、它将主导该器件上的 VCO。

输入基准的抖动是多少?所需的输出抖动限制是多少? 如果输入基准接近或低于限值、我们可以进一步工作以创建更理想的 PLL 配置。

此致!

CRIS