主题中讨论的其他器件: LMX2594、LMX2820

工具与软件:

大家好!

我想使用 LXK04832 PLL IC 为1.92MHz 时钟输出创建一个具有方波的连续时钟、但输出一个脉冲形状的波形、如随附的照片所示。

请帮助我了解为什么它会输出这样的结果。 附加的是 XX。 TCS 文件

谢谢。

e2e.ti.com/.../Second_5F00_LMK04832_5F00_config_5F00_240924.tcs

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好!

我想使用 LXK04832 PLL IC 为1.92MHz 时钟输出创建一个具有方波的连续时钟、但输出一个脉冲形状的波形、如随附的照片所示。

请帮助我了解为什么它会输出这样的结果。 附加的是 XX。 TCS 文件

谢谢。

e2e.ti.com/.../Second_5F00_LMK04832_5F00_config_5F00_240924.tcs

尊敬的 Kyu:

是否都锁定了 PLL?

您可以将 PLLx_LD_TYPE 设置为 PLLx DLD、如果锁定、每个 PLL 应设为高电平。

您是使用自己的定制电路板还是 EVM?

如果您使用的是 EVM -请确保您 在 LVDS 的输出端具有正确的终端。 默认情况下、该 EVM 针对不同的输出格式配置了不同的输出。

在边注-为什么不使用122.88MHz VCXO 而不使用100MHz?

这将 增加 PLL2的 PFD 并减小 N 分频器值、从而实现更好的 PN 性能。 您可以使用2949.12MHz VCO 频率(而不是2457.6MHz)来生成所需的输出。

此致、

Vicente

尊敬的 KB:

PLLx_LD 设置仅适用于输出到 IC 上 STATUS_LD 引脚的 PLLx_LD_Type。

我能否收到一份您的原理图?

此外、如果您需要2457.6MHz VCO 频率-可以使用122.88MHz VCXO 代替100MHz VCXO? PLL2的 PFD 将大得多、因此 N 分频器将降低、从而提高 PN 性能。

除此之外、我看不到您的配置有任何问题-一切看起来都正常。

如果您切换输出格式或检查不同的输出-是否会遇到同样的问题?

此致、

Vicente

您好、Vicente

关于 VCXO 变化、此处是 xx 的仿真结果。 TCS 和 xx.sim 更改至122.88MHz 后。

请检查以确保计算准确。

1. LMK04832.

- OSC_IN : 122.88MHz

- CLKin0 : 245.76MHz

2. LMX2594

- OSC_IN : 122.88MHz

- RFOUT A : 3.932.16MHz

- RFOUT B : 1.92MHz

此致、

kb

e2e.ti.com/.../PLL2_5F00_LMK04832_5F00_122.88_2D00_1031_2D00_t.tcse2e.ti.com/.../PLL3_5F00_LMX2594_5F00_122.88_2D00_1031_2D00_t.tcs

你好 Ryu、

对于 LMK04832、看上去一切正常。

我的问题是 LMX2820 -您真的需要36kHz 环路带宽吗?

我看到、在 PLLatinumSim 配置中、您已经针对该带宽对其进行了计算。

然而、我也会在 LMX2820输入路径中使用双倍输入、而不是分频器、这也会降低 N 分频器值、从而实现更好的 PN 性能。 我还看到了大量红色、因此我想假设这是错误配置的、因为 PFD_SEL 选项被禁用、并且 Pre-R Post-R、MULT、N 分频器和 VCO 值不正确。

请尝试以下操作。

此致、

Vicente

您好、Vicente

我们使用的器件是 LMX2594。 36kHz BW 在 Sim 工具中自动计算。

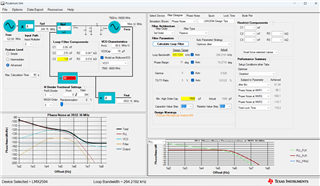

36kHz BW 是否存在问题? 请参考下图。

我们需要您提供有关 LMX2594环路滤波器值的帮助。 您能否向我们发送仿真结果 R、C?

此外、下面显示的工具与我们所拥有的工具 GUI 不同。 这是新版本吗?

如您所述、当我们将倍频器设置为 x2时、N 分频器变为红色、RFOUT 不会显示所需的值。

您也可以模拟此部件并提供结果吗?

请参考下图。

此致、

kb

您好、Vicente

我们使用的器件是 LMX2594。 36kHz BW 在 Sim 工具中自动计算。

36kHz BW 是否存在问题? 请参考下图。

我们需要您提供有关 LMX2594环路滤波器值的帮助。 您能否向我们发送仿真结果 R、C?

此外、下面显示的工具与我们所拥有的工具 GUI 不同。 这是新版本吗?

如您所述、当我们将倍频器设置为 x2时、N 分频器变为红色、RFOUT 不会显示所需的值。

您也可以模拟此部件并提供结果吗?

请参考下图。

此致、

kb

尊敬的 Kyu:

很抱歉、我加载了2820 -我的道歉。

如果可能、我会推荐以下配置。

在这种情况下、环路滤波器是稳定的。

实际上、我无法告诉您如何设计环路滤波器、因为环路带宽要求取决于您的应用。

例如、一些客户需要尽可能快的锁定时间、从而使环路带宽尽可能大。

而其他客户则需要极窄的环路带宽。

我会得到以下结果:

但是、正如我提到过的、我的方法是始终使 PFD 尽可能大、这将减少 N 分频器值、从而实现更好的 PN 性能。

如果您的应用需要54kHz 的环路带宽-环路 滤波器 是稳定的、但我会首先使用倍频器。

使用倍频器并设计54kHz 环路带宽如下所示:

此外-请忽略红色。

在 TICSpro 中、如果我们减少 MASH 顺序、N 分频器可以小于36。

此致、

Vicente

您好、Vicente

我们已使用122.88MHz 输入源确认 RFoutA 3932.16MHz 输出正常。 但是、RFoutB REF-CLK 1.92MHz 仍是一个问题。

我们有一个关于验证 RFoutB SYSREF CLK 1.92MHz 输出的请求。

您能否使用您拥有的 EVM 板为3932.16MHz 处的 RFoutA 和1.92MHz 处的 RFoutB 提供实际波形测量结果?

下图显示了我们电路板的完整 PLL 时钟方框图。

请您参考并通过仿真确认所需的时钟、然后将结果发送给我们。

很长一段时间已经延迟、因此我们希望您能及时作出响应。

此致、

kb

尊敬的 KB:

我想我看到了你的问题。

当使用 LMX2594的 SYSREF 输出时、需要设置 VCO_PHASE_SYNC 位。

启用该位会将 IncludedDivide 值从1更改为4、因为需要将输出分频器设置为2才能生成3932.16MHz

这也将总体 N 分频器值(现在减少到7)降低到 MASH 顺序不能支持的数字、因为任何调制器的最小 N 分频器值都必须为28。

遗憾的是、LMX2594将无法生成1.92MHz 输出。

此致、

Vicente

嗨、Kyu、

我进入实验室并测试了这些。

我设法使 LMX2594锁定并获得了1.92MHz SYSREFOUT。

e2e.ti.com/.../1.92MHz - SYSREFOUT.TCS

我只是连接到示波器 SE、而没有端接未使用的端、但是仍然只想证明其功能、器件锁定和输出是正确的。

此致、

Vicente

Kyu、您好!

我已经在工作台上检查过它。

尝试此配置。

此致、

Vicente

e2e.ti.com/.../LMK04832_5F00_245.76MHz KIN1_5F00_122.88MHZOSCIN_5F00_2949.12MHZVCO.TCS

您好、 Vicente

我有一个关于 LMK04832的问题。

输入 Fosc 为10MHz、Fpd 为0.4MHz、Fvco 为2457.6MHz、而 Fout 为245.76MHz。

当使用示波器同时测量输出频率和基准频率时、输出频率应保持与10MHz 的基准时钟同步。 但是、同步未保持、并且输出频率在参考点不保持稳定、但会波动。

附件为 xxx.tcs 文件和 PLLatinum 捕获图像、供您参考。

非常感谢您的建议。

此致、

kb

e2e.ti.com/.../LMK04832_5F00_PLL1_5F00_20241116.tcs

尊敬的 Kyu:

您最初说过这一点。

CLKinX 为245.76MHz -这是有效的、因为 R 分频器将为2 * N 分频器、因此 fOSC 是122.88MHz、这将导致锁定。

如果要清除抖动、则需要使用具有非常窄的环路带宽的 PLL1来实现、以允许 VCXO 噪声占主导地位。

但您需要有一个 CLKINx 频率、该频率可以以整数关系驱动122.88MHz 外部 VCXO。

无法通过10MHz 输入驱动外部122.88MHz VCXO。

必须满足以下数学关系、其中 fVCO = 122.88MHz & fOSC = 10MHz、且 N 和 R 都为 整数 平均值。

我觉得很难相信你已经锁定在 PLL1。

由 PLL1驱动的122.88MHz 外部 VCXO 会馈送到 OSCIN 以进行 CLK 分配- PLL2的 PFD 为2457.6MHz。

您可以将10MHz 输入直接输入到 OSCIN 以生成2457.6MHz VCO 频率、方法是在单环路模式下运行 LMK04832、但不再需要进行抖动清除、并且您的输出相位噪声将受到干扰-您可以在您共享的 PLLatinumSim 屏幕截图中看到、其中的 FPD 频率非常低、N 分频器非常大(6144)。

如果您希望使用 PLL1清除抖动以驱动外部122.88MHz VCXO、则需要确保 fOSC 的值符合上面发送的公式中的整数关系。

您无法使用10MHz 完成此操作。

此致、

Vicnete.

您好、Vicente

请确认您找到的 PLL R&N 分频器是否符合以下条件:

如果上述条件正确、这是否意味着只能在双环路模式下满足这些条件、在单环路模式下不能满足这些条件?

在单环路模式下、是否有办法满足以下条件?

非常感谢您的建议。

此致

kb