工具与软件:

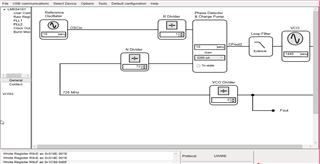

我正在使用的时钟发生器具有两个 PLL。 PLL2完全锁定、但 PLL1无法锁定 .

以下是我所需的时钟频率设置。 GEN.

PLL1:

PLL2:

我们首先使用了推荐的环路滤波器设计、即

后来尝试将带宽增加到17kHz、但这也没有帮助

无法真正理解为什么 PLL1未锁定。 请提供帮助

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、Micheal、

我们观察到该器件能够提供稳定的时钟、但频率与我们配置的频率不完全相同。

例如:预期频率为30 MHz 测量输出为30.8 MHz。

这也会在下电上电时发生变化。

我们确实尝试了将 BW 增加到17KHz、但没有看到任何改进。

寄存器映射、