请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK00301 工具与软件:

尊敬的专家:

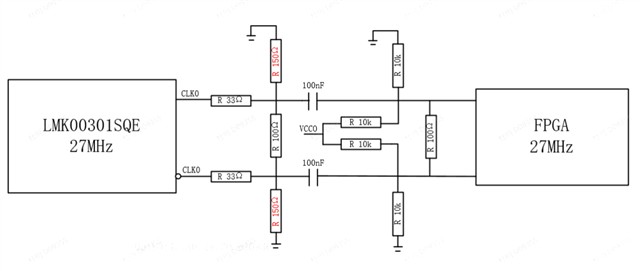

设计原理图如下、设计原理图如下。 我们的电流 FPGA 设计要求为:100mV~600mV 的差分输入电压范围、300mV~1125mV 的共模输入电压范围、-200mV-1200mV 的单端输入电压过冲范围。 我们希望查询一下时钟阻抗匹配电路的设计、以便获得解答。 谢谢您~

1.我们是否需要150 Ω 电阻器来将交流耦合电容器接地?

2、布置单块印刷电路板时,是否需要将发送端和接收端的匹配电路分别放置在端口附近? 交流耦合电容器是否也应放置在靠近发送端的位置?