Thread 中讨论的其他器件:LMX2594

工具与软件:

您好!

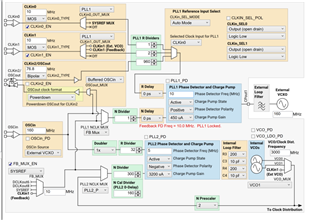

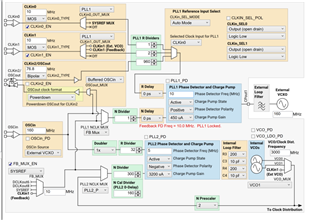

我将使用 Xilinx 的 CLK104电路板、其中包含 LMK04828B 和 LMX2594 PLL、再次从 Xilinx 驱动 ZCU208评估板中的时钟。 CLK104板还具有3个输入参考时钟选项:板载 TCXO、SMA 输入、从 FPGA 恢复的时钟。

所以、我想通过 CLK104的 SMA 输入为 LMK 使用外部参考时钟输入、而不使用 CLK104的板载10MHz TCXO。 我使用 TICS pro 应用程序仅选择 CLKin0作为 PLL1输入、即使我没有在 SMA 输入处提供任何参考时钟、我仍然可以看到 LMK 在输出端输出500MHz 时钟(DCLKout0和6、如编程)。 不过、为 LMK 启用了保持模式(不确定这是否与相关)

非常感谢这里的任何帮助。 谢谢!